Intel

®

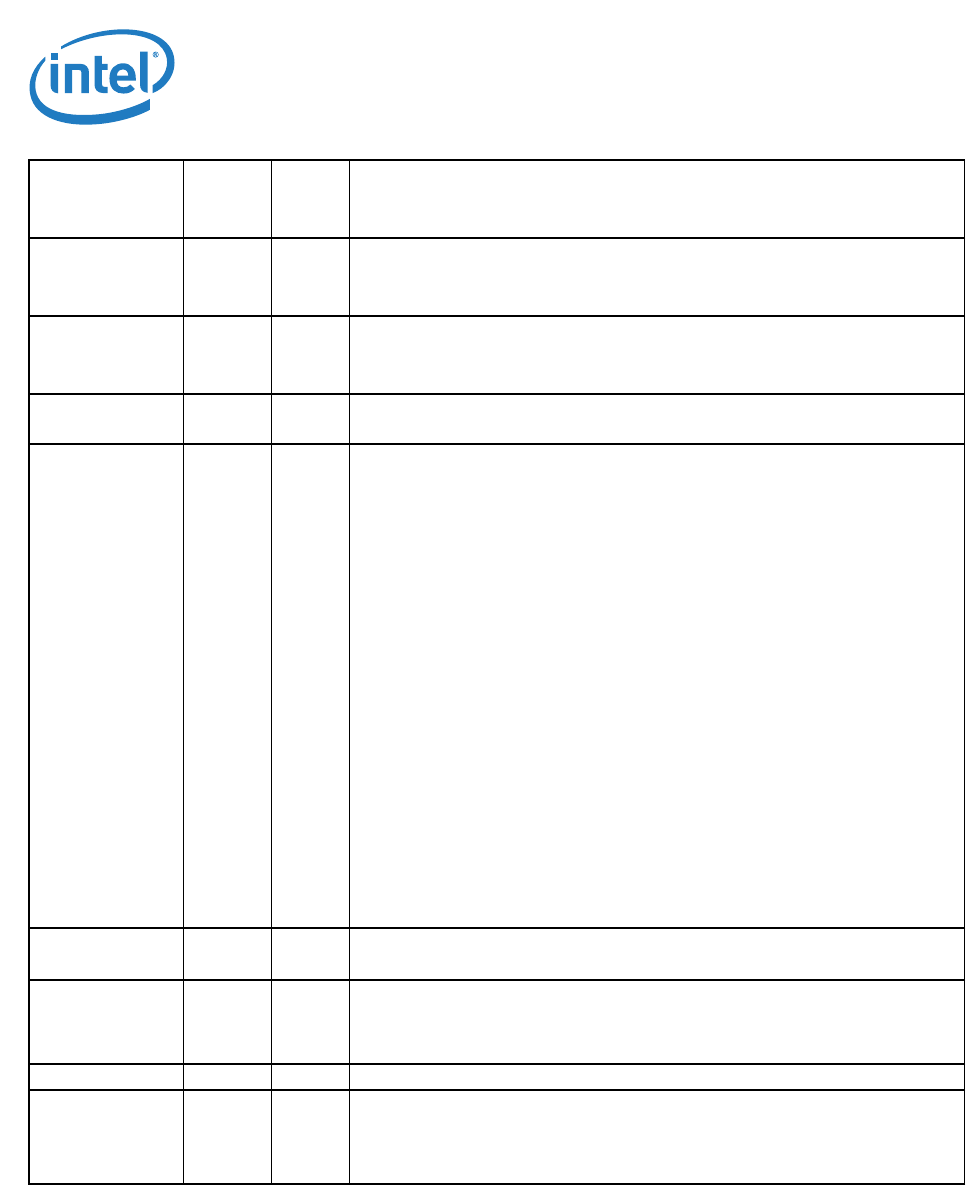

82575EB Gigabit Ethernet Controller — Firmware Semaphore - FWSM (05B58h; R/WS)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

412 January 2011

PHY_SERDES1_

Config_Err_Ind

27 0h PHY/SerDes1 configuration error indication

Set to 1b by firmware when it fails to configure LAN1 PHY/SerDes.

Cleared by firmware upon successful configuration of LAN1 PHY/SerDes.

PHY_SERDES0_

Config_Err_Ind

26 0h PHY/SerDes0 configuration error indication

Set to 1b by firmware when it fails to configure LAN0 PHY/SerDes.

Cleared by firmware upon successful configuration of LAN0 PHY/SerDes.

PCIe*_

Config_Err_

Ind

25 0h PCIe* configuration error indication

Set to 1b by firmware when it fails to configure PCIe* interface.

Cleared by firmware upon successful configuration of PCIe* interface.

Field Bit(s)

Initial

Value

Description

Ext_Err_Ind 24:19 0h External error indication

Firmware writes here the reason that the firmware has reset / clock gated. For

example, EEPROM, flash, patch corruption, etc.

Possible values:

00h: No Error

01h: Invalid EEPROM checksum

02h: Unlocked secured EEPROM

03h: Clock Off host command

04h: Invalid FLASH checksum

05h: C0 checksum failed

06h: C1 checksum failed

07h: C2 checksum failed

1

08h: C3 checksum failed

09h: TLB table exceeded

0Ah: DMA load failed

0Bh: Bad hardware version in patch load

0Ch: Flash device not supported

0Dh: Unspecified Error

3Fh: Reserved - max error value.

Reset_Cnt 18:16 0h Reset Counter

Firmware increments the count at every reset.

FW_Val_Bit 15 0h Firmware Valid Bit

Hardware clears this bit in reset de-assertion so software can know firmware mode

(bits 1-5) is invalid. Firmware should set this bit to 1b when it is ready (end of boot

sequence).

Reserved 14:7 0h Reserved

EEP_Reload_

Ind

6 0h EEPROM reloaded indication

Set to 1b after firmware reloads the EEPROM.

Cleared by firmware once the “Clear Bit” host command is received from host

software.