Intel

®

82575EB Gigabit Ethernet Controller — Legacy Receive Descriptor Format

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

104 January 2011

If for any queue SRRCTL[n].BSIZEPACKET equals 0b, the buffer size defined by RCTL.BSIZE is used;

otherwise, the buffer size defined by SRRCTL[n].BSIZEPACKET is used.

In addition, for advanced descriptor usage the SRRCTL.BSIZEHEADER field is used to define the size of

the buffers allocated to headers.

The 82575 places no alignment restrictions on receive memory buffer addresses. This is desirable in

situations where the receive buffer was allocated by higher layers in the networking software stack, as

these higher layers might have no knowledge of a specific device's buffer alignment requirements.

Note: When the No Snoop Enable bit is used in advanced descriptors, the buffer address must be

16-bit aligned.

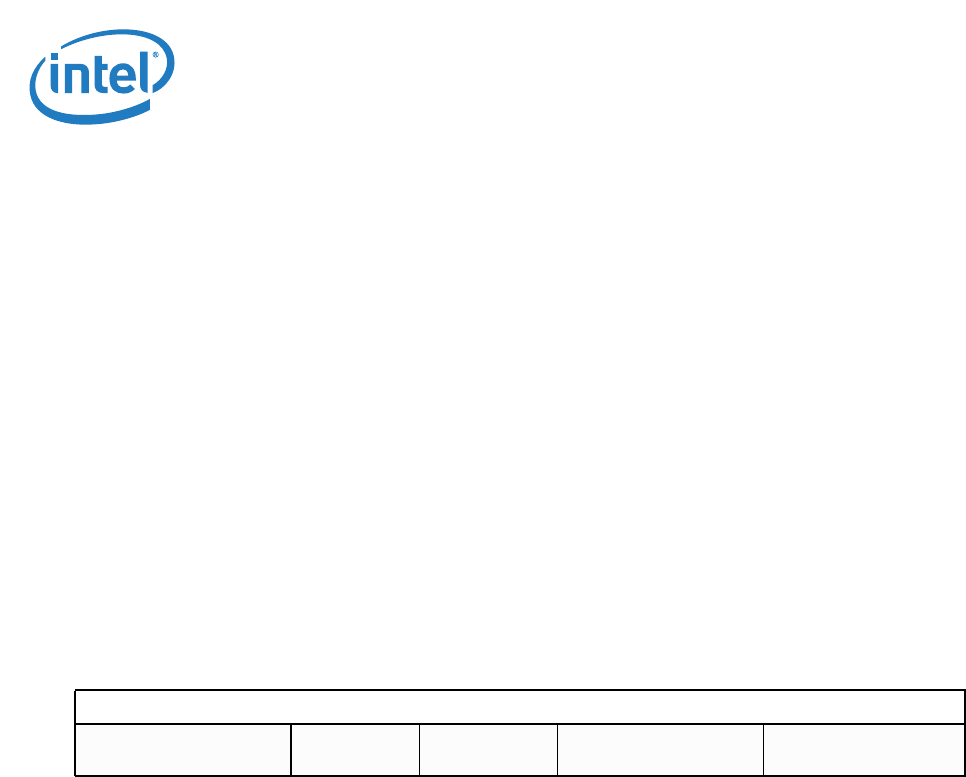

5.3.3 Legacy Receive Descriptor Format

A receive descriptor is a data structure that contains the receive data buffer address and fields for

hardware to store packet information. If SRRCTL[n].DESCTYPE = 000b, the 82575 uses the Legacy Rx

Descriptor as shown in Table 27. The shaded areas indicate fields that are modified by hardware upon

packet reception (descriptor write-back).

Table 27. Receive Descriptor (RDESC) Layout

Note: The checksum indicated here is the unadjusted “16-bit ones complement” of the packet. A

software assist might be required to back out appropriate information prior to sending it to

upper software layers. The packet checksum is always reported in the first descriptor (even

in the case of multi-descriptor packets).

5.3.3.1 Length Field

Upon receipt of a packet for the 82575, hardware stores the packet data into the indicated buffer and

writes the length, Packet Checksum, status, errors, and status fields. Length covers the data written to

a receive buffer including CRC bytes (if any). Software must read multiple descriptors to determine the

complete length for packets that span multiple receive buffers.

5.3.3.2 Packet Checksum

For standard 802.3 packets (non-VLAN) the Packet Checksum is by default computed over the entire

packet from the first byte of the DA through the last byte of the CRC, including the Ethernet and IP

headers. Software can modify the starting offset for the packet checksum calculation via the Receive

Checksum Control register (RXCSUM). To verify the TCP/UDP checksum using the Packet Checksum,

software must adjust the Packet Checksum value to back out the bytes that are not part of the true TCP

Checksum. When operating with the Legacy Rx Descriptor, the RXCSUM.IPPCSE and RXCSUM.PCSD

fields should be cleared (the default value).

63 48 47 40 39 32 31 16 15 0

0

Buffer Address [63:0]

8

VLAN Tag Errors Status 0 Packet Checksum

(See Note)

Length