VLAN Filter Table Array - VFTA (05600h + 4*n [n=0..127]; R/W) — Intel

®

82575EB Gigabit

Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 381

14.5.4 VLAN Filter Table Array - VFTA (05600h + 4*n

[n=0..127]; R/W)

There is one register per 32 bits of the VLAN Filter Table. The size of the word array depends on the

number of bits implemented in the VLAN Filter Table. Software must mask to the desired bit on reads

and supply a 32-bit word on writes.

Note: All accesses to this table must be 32 bit.

The algorithm for VLAN filtering using the VFTA is identical to that used for the Multicast Table Array.

Refer to Section 14.5.1 for a block diagram of the algorithm. If VLANs are not used, there is no need to

initialize the VFTA.

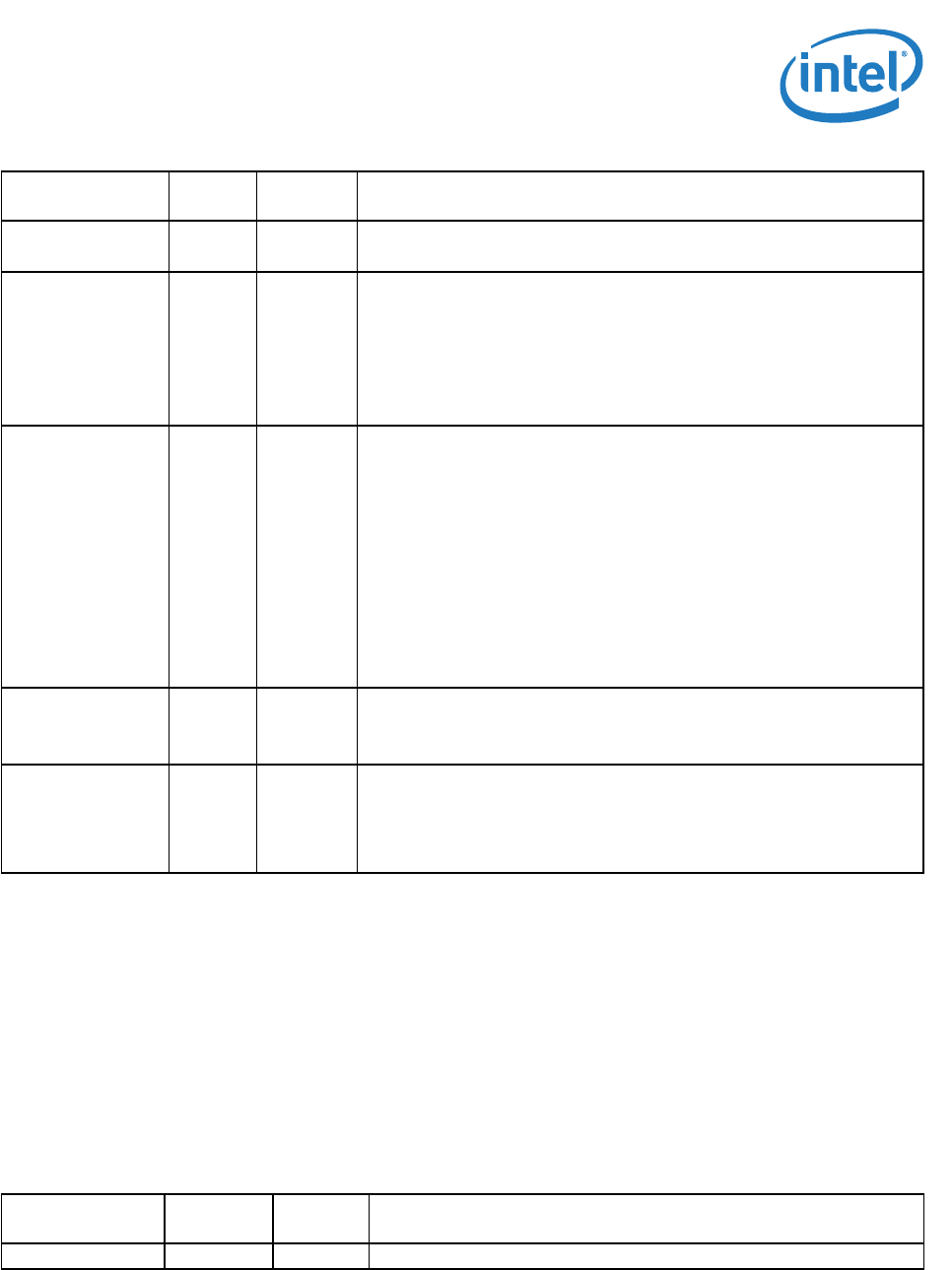

Field Bit(s)

Initial

Value

Description

RAH 15:0 X Receive address High

Contains the upper 16 bits of the 48-bit Ethernet address.

ASEL 17:16 X Address Select

Selects how the address is to be used in the address filtering.

00b = Destination address (required for normal mode)

01b = Source address

10b = Reserved

11b = Reserved

QSEL 19:18 00b Queue Select

Association through MAC address - selects one of the four receive queues for

packets matching this destination address.

00b = Queue 0

01b = Queue 1

10b = Queue 2

11b = Queue 3

Association through MAC address + RSS - serves as a pool bit, identifying the

target pool:

QSEL[19] = 0b - pool 0

QSEL[19] = 1b - pool 1

Reserved 30:20 0b Reserved

Reads as 0b.

Ignored on writes.

AV 31 Address Valid

Cleared after master reset. If an EEPROM is present, the Address Valid field of

the Receive Address Register 0 is set to 1b after a software or PCI reset or

EEPROM read.

In entries 0-15 this bit is cleared by master reset.

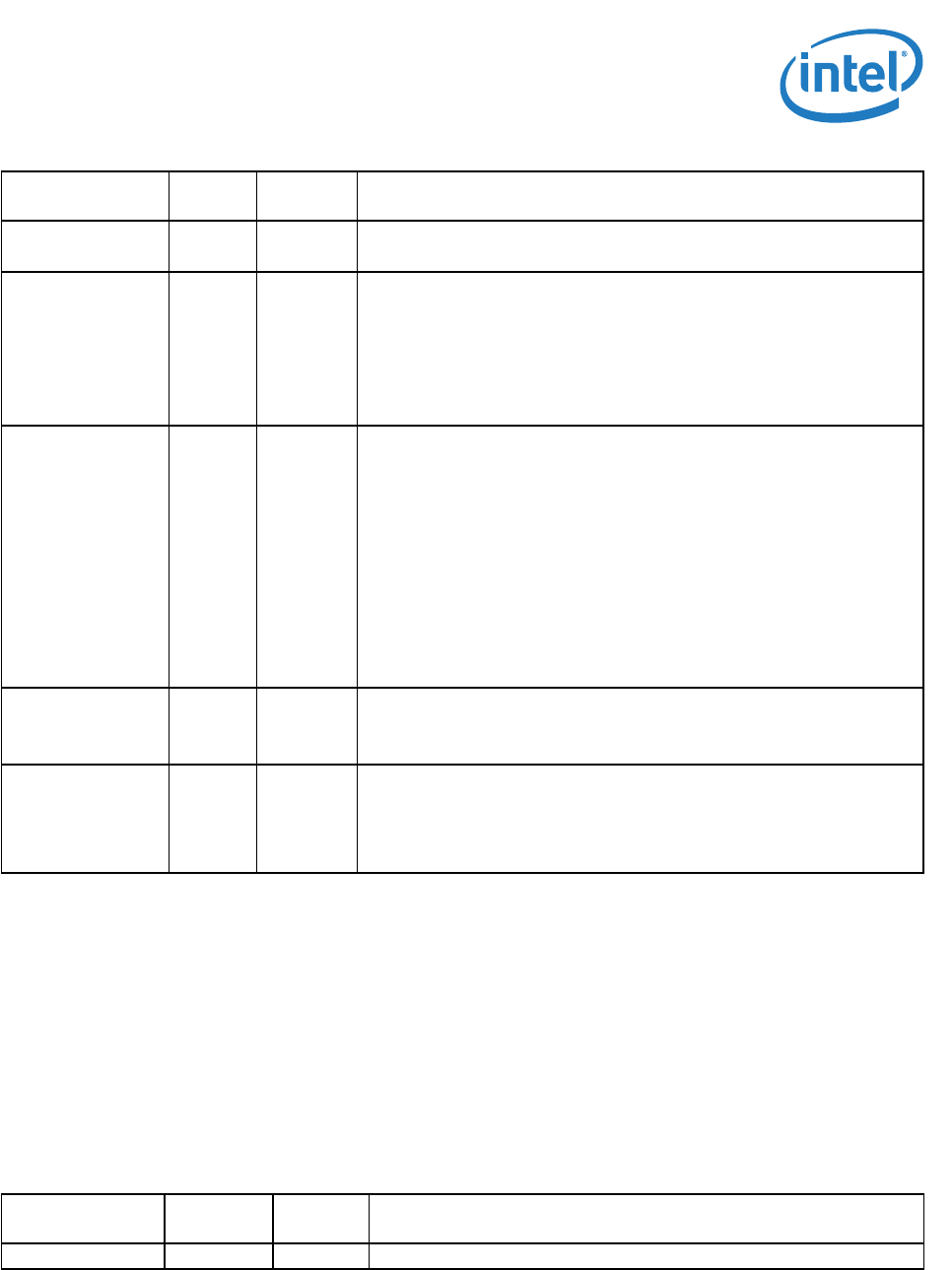

Field Bit(s)

Initial

Value

Description

Bit Vector 31:0 X Double-word wide bit vector specifying 32 bits in the VLAN Filter table.