Transmit Data FIFO Tail Register - TDFT (03418h; R/WS) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 435

14.10.9 Transmit Data FIFO Tail Register - TDFT

(03418h; R/WS)

This register stores the head of the on–chip transmit data FIFO. Since the internal FIFO is organized in

units of 64-bit words, this field contains the 64-bit offset of the current Transmit FIFO Tail. A value of 8h

in this register corresponds to an offset of 8 Qwords into the Transmit FIFO space. This register is

available for diagnostic purposes only, and should not be written during normal operation.

14.10.10 Transmit Data FIFO Head Saved Register -

TDFHS (03420h; R/WS)

This register stores a copy of the Transmit Data FIFO Head register in case that internal register needs

to be restored. This register points to the header of the last packet in the packet buffer, even if it was

already transmitted. This register is available for diagnostic purposes only, and should not be written

during normal operation.

14.10.11 Transmit Data FIFO Tail Saved Register - TDFTS

(03428h; R/WS)

This register stores a copy of the Transmit Data FIFO Tail register in case the internal register needs to

be restored. This register points to the tail of the last packet in the packet buffer, even if it was already

transmitted. This register is available for diagnostic purposes only, and should not be written during

normal operation.

FIFO Head 12:0 0b Transmit FIFO Head pointer. Note that the initial value equals PBA.RXA times 128.

Reserved 30:13 10000h Reads as 0b. Should be written to 0b for future compatibility.

Tx Memory Full 31 0b Tx FIFO memory full indication.

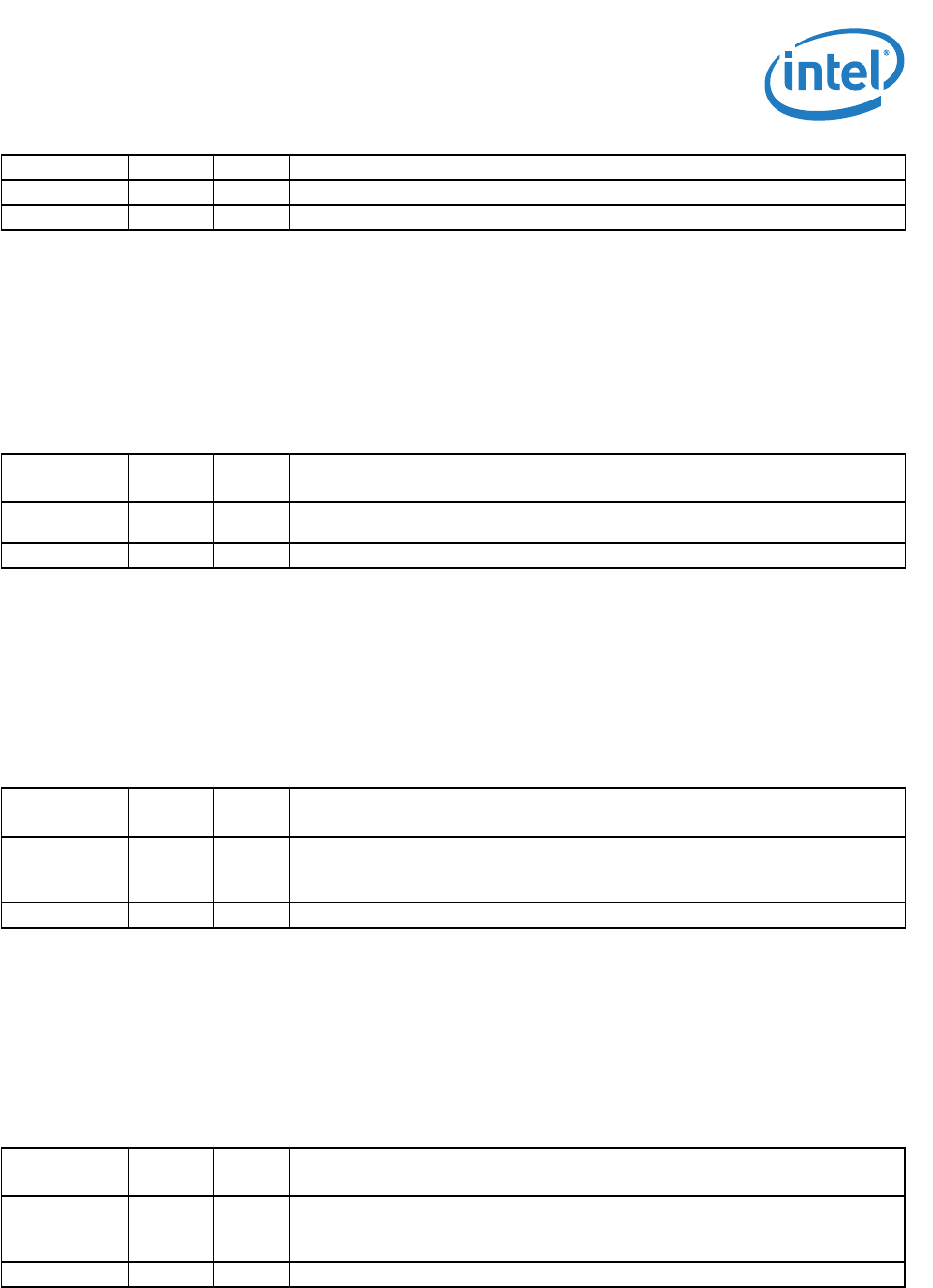

Field Bit(s)

Initial

Value

Description

FIFO Tail 12:0 0h Transmit FIFO tail pointer. Note that after reset, the initial value is 0b. After Tx is

enabled, the initial value equals PBA.RXA times 64.

Reserved 31:13 0h Reads as 0b. Should be written to 0b for future compatibility.

Field Bit(s)

Initial

Value

Description

FIFO Head 12:0 0b Transmit FIFO Last Packet Header Pointer

Note that after reset, the initial value is 0b. After Tx is enabled, initial value equals

PBA.RXA times 64.

Reserved 31:13 0b Reads as 0b. Should be written to 0b for future compatibility.

Field Bit(s)

Initial

Value

Description

FIFO Tail 12:0 0b Transmit FIFO Last Packet Tail Pointer

Note that after reset, the initial value is 0b. After Tx is enabled, initial value equals

PBA.RXA times 64.

Reserved 31:13 0b Reads as 0b. Should be written to 0b for future compatibility.