Intel

®

82575EB Gigabit Ethernet Controller — 82575 and SerDes Power-Down State

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

230 January 2011

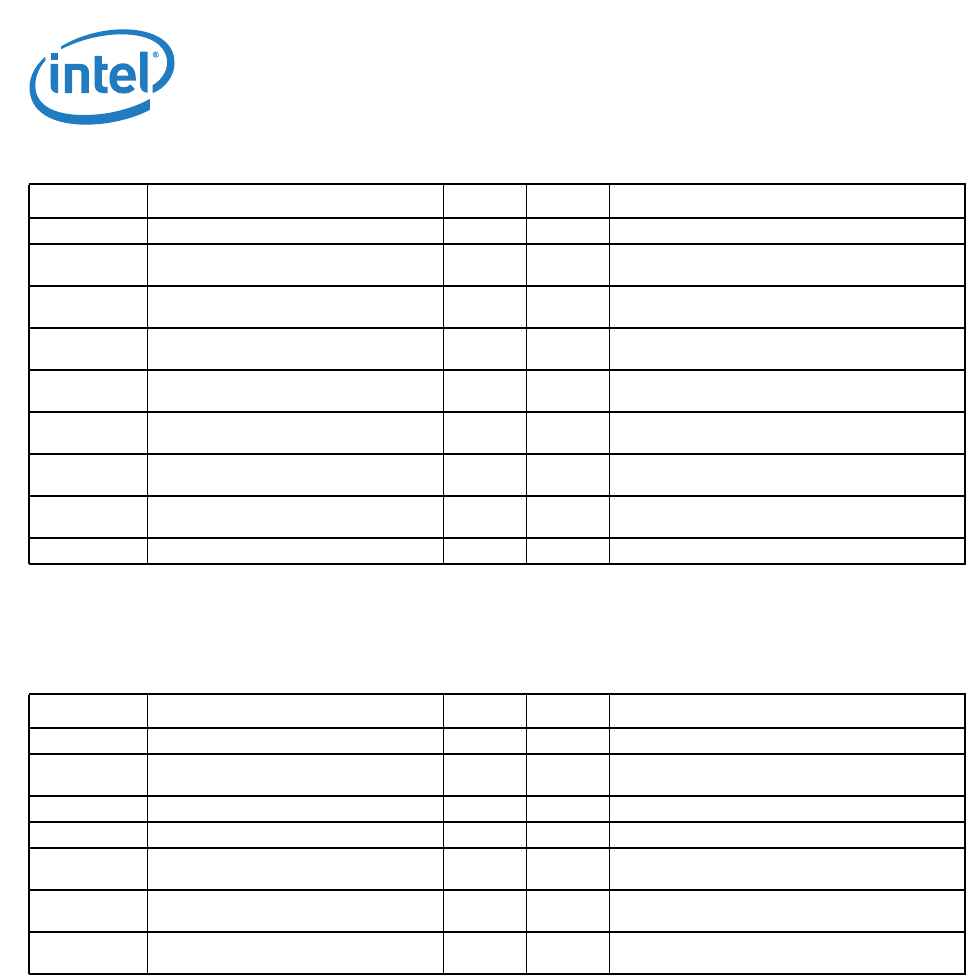

7.4.2.6 Timing Guarantees

The 82575 guarantees the following start up and power state transition related timing parameters.

7.4.3 82575 and SerDes Power-Down State

7.4.3.1 SerDes Power-Down State

The SerDes enters a power-down state when none of its clients is enabled and therefore, no need to

maintain a link. The following conditions must be met for the SerDes to enter a power-down mode:

• SerDes power-down is enabled through either the EEPROM SerDes Low Power Enable bit or the

same bit in CTRL_EXT.

• The LAN function associated with this SerDes is in a non-D0 state.

• APM WOL is inactive.

• ACPI PME is disabled for both LAN functions (in some Dr cases, ACPI power management is

irrelevant).

Parameter Description Min Max Notes

t

xog

Xosc stable from power stable. 10 ms

t

PWRGDPE_RST

-CLK

PCIe* clock valid to PCIe* power

good.

100 μs - As per PCIe* Specification.

t

PVPGL

Power rails stable to PCIe* PE_RST_N

in active

100 ms - As per PCIe* Specification.

T

pgcfg

External PE_RST_N signal to first

configuration cycle.

100 ms As per PCIe* Specification.

t

d0mem

82575 programmed from D3hot to D0

state to next 82575 access.

10 ms As per PCIe* Management Specification.

t

l2pg

L2 link transition to PE_RST_N de-

assertion.

0 ns As per PCIe* Specification.

t

l2clk

L2 link transition to removal of PCIe*

reference clock.

100 ns As per PCIe* Specification.

T

clkpg

PE_RST_N de-assertion to removal of

PCIe* reference clock.

0 ns As per PCIe* Specification.

T

pgdl

PE_RST_N assertion time. 100 μs As per PCIe* Specification.

Parameter Description Min Max Notes

t

xog

Xosc stable from power stable. 10 ms

t

ppg

Internal power good delay from valid

power rail.

35 ms 35ms

t

ee

EEPROM read duration. - 20 ms

t

ppg-clkint

PCIe* PE_RST_N to internal PLL lock. 50 μs

t

clkpr

Internal PCIe* PE_RST_N from

external PCIe* PE_RST_N.

50 μs

t

pgtrn

PCIe* PE_RST_N to start of link

training.

20 ms As per PCIe* Specification.

T

pgres

External PE_RST_N response to first

configuration cycle.

1 s As per PCIe* Specification.