Intel

®

82575EB Gigabit Ethernet Controller — Extended Interrupt Mask Set/Read - EIMS

(01524h; RWS)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

346 January 2011

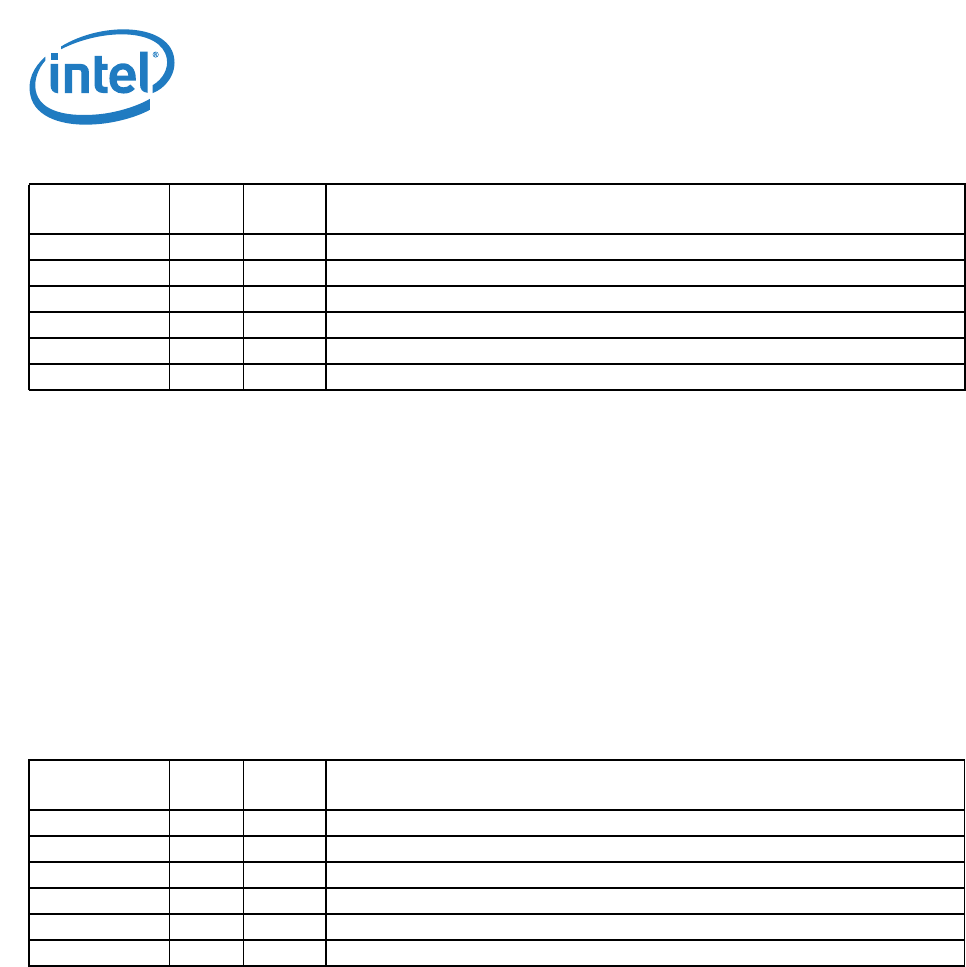

14.3.41 Extended Interrupt Mask Set/Read - EIMS

(01524h; RWS)

Reading of this register returns which bits have an interrupt mask set. An interrupt in EICR is enabled if

its corresponding mask bit is set to 1b and disabled if its corresponding mask bit is set to 0b. A PCI

interrupt is generated each time one of the bits in this register is set and the corresponding interrupt

condition occurs (subject to throttling). The occurrence of an interrupt condition is reflected by having a

bit set in the Extended Interrupt Cause Read register.

An interrupt might be enabled by writing a 1b to the corresponding mask bit location (as defined in the

ICR register) in this register. Any bits written with a 0b are unchanged. As a result, if software needs to

disable an interrupt condition that had been previously enabled, it must write to the Extended Interrupt

Mask Clear register rather than writing a 0b to a bit in this register.

14.3.42 Extended Interrupt Mask Clear - EIMC (01528h;

WO)

This register provides software a way to disable certain or all interrupts. Software disables a given

interrupt by writing a 1b to the corresponding bit in this register.

On interrupt handling, the software device driver should set all the bits in this register related to the

current interrupt request even though the interrupt was triggered by part of the causes that were

allocated to this vector.

Interrupts are presented to the bus interface only when the mask bit is set to 1b and the cause bit is

set to 1b. The status of the mask bit is reflected in the Extended Interrupt Mask Set/Read register and

the status of the cause bit is reflected in the Interrupt Cause Read register.

Field Bit(s)

Initial

Value

Description

RxQ 3:0 0000b Sets the corresponding EICR RxQ interrupt condition.

Reserved 7:4 0000b Reserved

TxQ 11:8 0000b Sets the corresponding EICR TxQ interrupt condition.

Reserved 29:12 0h Reserved

TCP Timer 30 0b Sets the corresponding EICR TCP interrupt condition.

Reserved 31 0b Reserved

Field Bit(s)

Initial

Value

Description

RxQ 3:0 0000b Mask bit for the corresponding EICR RxQ interrupt condition.

Reserved 7:4 0000b Reserved

TxQ 11:8 0000b Mask bit for the corresponding EICR TxQ interrupt condition.

Reserved 29:12 0h Reserved

TCP Timer 30 0b Mask bit for the corresponding EICR TCP timer interrupt condition.

Other Cause 31 1b Mask bit for the corresponding EICR other cause interrupt condition.