PCS Link Control - PCS_LCTL (04208h; R/W) — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 371

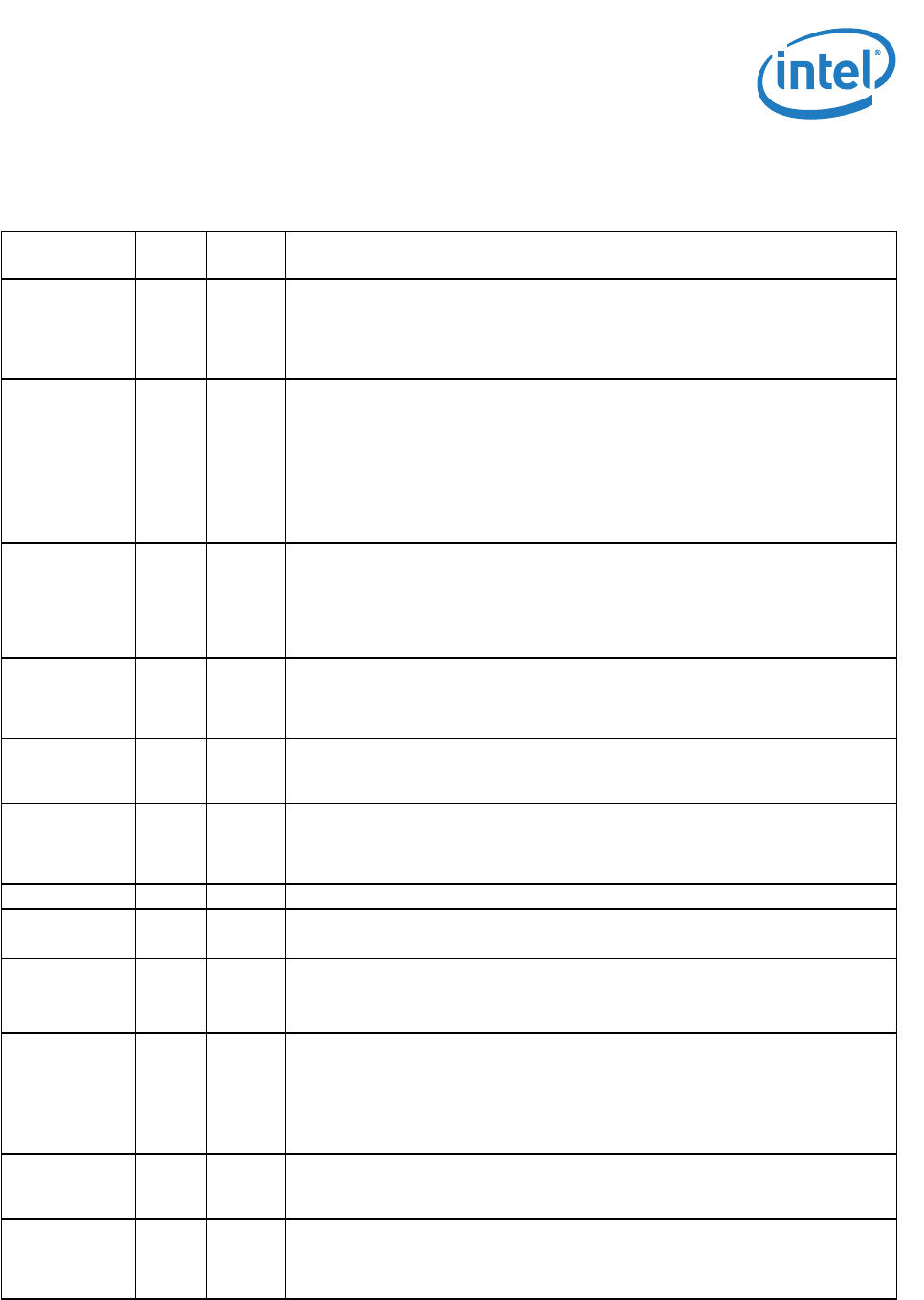

14.3.77 PCS Link Control - PCS_LCTL (04208h; R/W)

Field Bit(s)

Initial

Value

Description

FLV 0 0b Forced Link Value

This bit denotes the link condition when force link is set.

0b = Forced link down.

1b = Forced link up.

FSV 2:1 10b Forced Speed Value

These bits denote the speed when force speed and duplex is set. This value is also used

when AN is disabled or when in SerDes mode.

00b = 10 Mb/s (SGMII).

01b = 100 Mb/s (SGMII).

10b = 1000 Mb/s (SerDes/SGMII).

11b = Reserved.

FDV 3 1b Forced Duplex Value

This bit denotes the duplex mode when force speed and duplex is set. This value is also

used when AN is disabled or when in SerDes mode.

1b = Full duplex (SerDes/SGMII).

0b = Half duplex (SGMII).

FSD 4 0b Force Speed and Duplex

If this bit is set, then speed and duplex mode is forced to forced speed value and forced

duplex value, respectively. Otherwise, speed and duplex mode are decided by internal

AN/SYNC state machines.

FORCE LINK 5 0b Force Link

If this bit is set, then the internal LINK_OK variable is forced to forced link value (bit 0

of this register). Otherwise, LINK_OK is decided by internal AN/SYNC state machines.

LINK LATCH

LOW

6 0b Link Latch Low Enable

If this bit is set, then link OK going LOW (negative edge) is latched until a processor

read. Afterwards, link OK is continuously updated until link OK again goes LOW

(negative edge is seen).

Reserved 15:7 - Reserved

AN_ENABLE 16 0b

1

AN Enable

Setting this bit enables the AN process.

AN RESTART 17 0b AN Restart

Setting this bit restarts the AN process.

This bit is self clearing.

AN TIMEOUT EN 18 1b AN Timeout Enable

This bit enables the AN Timeout feature. During AN, if the link partner does not respond

with AN pages, but continues to send good IDLE symbols, then LINK UP is assumed.

(This enables LINK UP condition when link partner is not AN-capable and does not

affect otherwise).

This bit should not be set in SGMII mode.

AN SGMII

BYPASS

19 0b AN SGMII Bypass

If this bit is set, then IDLE detect state is bypassed during AN in SGMII mode. This

reduces the acknowledge time in SGMII mode.

AN SGMII

TRIGGER

20 0B AN SGMII Trigger

If this bit is cleared, then AN is not automatically triggered in SGMII mode even if SYNC

fails. AN is triggered only in response to PHY messages or by a manual setting like

changing the AN Enable/Restart bits.