PCIe* Control - GCR (05B00h; R) — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 401

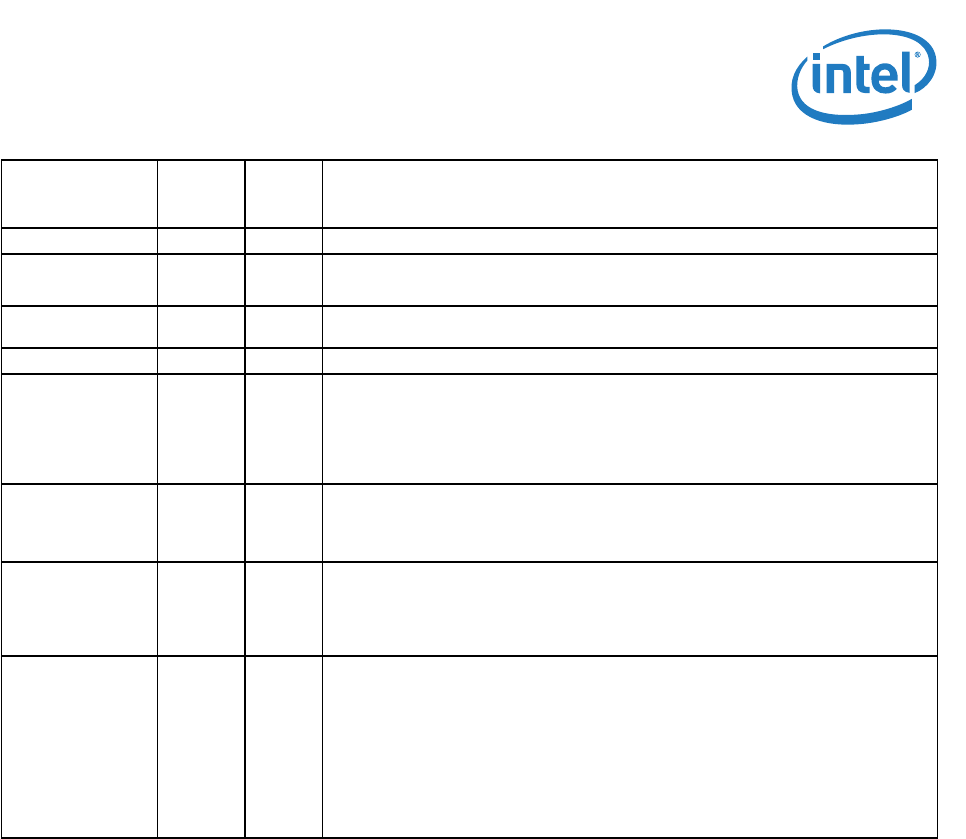

L0s_Entry_Lat 24 0b L0s Entry Latency

Set to 0b to indicate L0s entry latency is the same as L0s exit latency. Set to 1b to

indicate L0s entry latency is (L0s exit latency/4).

Reserved 23 0b Reserved

Reserved 22 1b Reserved

Must be set to 1b.

hdr_log Inversion 21 0b If set, the header log in error reporting is written as 31:0 to log1, 63:643 in log2. If

not set, the header is written as 127:96 in log1 95:64 in log 2 …..

PBA_CL_DEAS 20 0b If cleared, PBA is cleared on de-assertion of MSI-X request.

g_sa_250_2ph_en 19 0b Enables probed-data speed reduction to enable slow pads reflect 250 Mbaud signals

by splitting them into two phases, each 62.5 Mbaud. Effective only in GIO analog

standalone mode.

1b = enable (default).

0b = disabled.

PCIe* Capability

Version (RO)

18 0b Reports the PCIe* Capability Version Supported

0b = Capability version = 1h.

1b = Capability version = 2h.

Completion_

Timeout_Disable

(RO or RW1)

17 0b Indicates if PCIe* Completion Timeout is Supported (after an

Internal_Power_On_Reset)

0b = Completion timeout enabled.

1b = Completion timeout disabled.

Completion_

Timeout_Resend

16 1b When set, enables to resend a request once the completion timeout expired

0b = Do not resend request on completion timeout.

1b = Resend request on completion timeout.

This bit is used no matter which timeout mechanism is used.