Intel

®

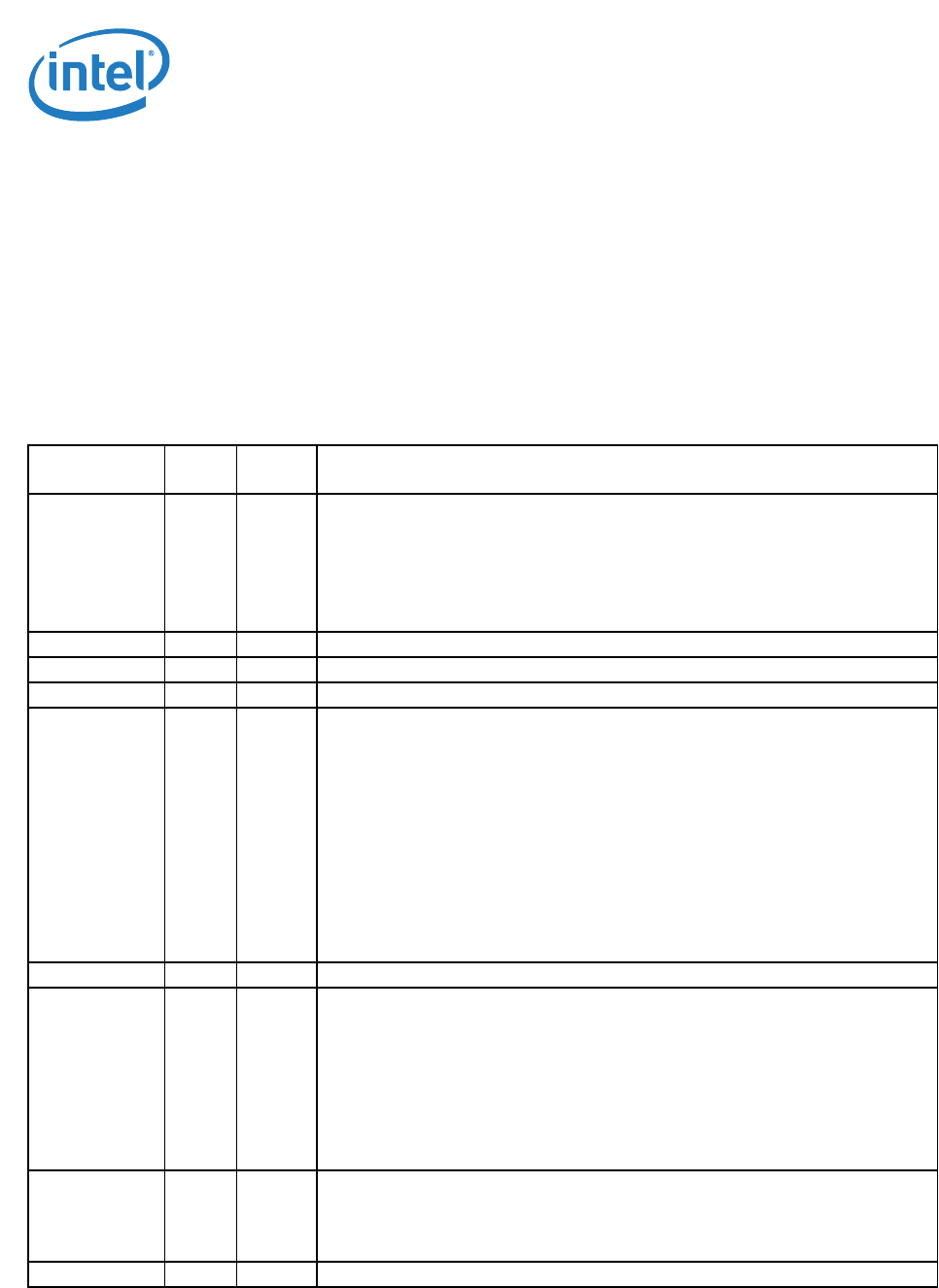

82575EB Gigabit Ethernet Controller — Receive Descriptor Control - RXDCTL (02828h +

100*n [n=0..3]; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

360 January 2011

14.3.60 Receive Descriptor Control - RXDCTL (02828h +

100*n [n=0..3]; R/W)

This register controls the fetching and write-back of receive descriptors. The three threshold values are

used to determine when descriptors are read from and written to host memory. The values are in units

of descriptors (each descriptor is 16 bytes).

• Queue0 - RXDCTL0 (02828h)

• Queue1 - RXDCTL1 (02928h)

• Queue2 - RXDCTL2 (02A28h)

• Queue3 - RXDCTL3 (02B28h)

Field Bit(s)

Initial

Value

Description

PTHRESH 5:0 00h Prefetch Threshold

PTHRESH is used to control when a prefetch of descriptors is considered. This threshold

refers to the number of valid, unprocessed receive descriptors the 82575 has in its on-

chip buffer. If this number drops below PTHRESH, the algorithm considers pre-fetching

descriptors from host memory. This fetch does not happen unless there are at least

HTHRESH valid descriptors in host memory to fetch.

Note: HTHRESH should be given a non zero value each time PTHRESH is used.

Reserved 7:6 00h Reserved

HTHRESH 13:8 00h Host Threshold

Reserved 15:14 00h Reserved

WTHRESH 21:16 01h Write-Back Threshold

WTHRESH controls the write-back of processed receive descriptors. This threshold

refers to the number of receive descriptors in the on-chip buffer that are ready to be

written back to host memory. In the absence of external events (explicit flushes), the

write-back occurs only after at least WTHRESH descriptors are available for write-back.

Possible values:

PTHRESH = 0, 47

WTHRESH = 0, 63

HTHRESH = 0, 63

Note: Since the default value for write-back threshold is 1b, the descriptors are

normally written back as soon as one cache line is available. WTHRESH must contain a

non-zero value to take advantage of the write-back bursting capabilities of the 82575.

Reserved 24:22 00h Reserved

ENABLE 25 1/0b Receive Queue Enable

When set, the Enable bit enables the operation of the specific receive queue.

1b = Default value for queue 1.

0b = Default value for queue 3:0.

Setting this bit initializes all internal registers of the specific queue. Until then, the state

of the queue is kept and can be used for debug purposes.

When disabling a queue, this bit is cleared only after all activity in the queue has

stopped.

SWFLUSH (WC) 26 0b Receive Software Flush

Enables software to trigger receive descriptor write-back flushing, independently of

other conditions.

This bit is cleared by hardware.

Reserved 31:27 00h Reserved