Intel

®

82575EB Gigabit Ethernet Controller — SERDES ANA - SERDESCTL (00024h; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

326 January 2011

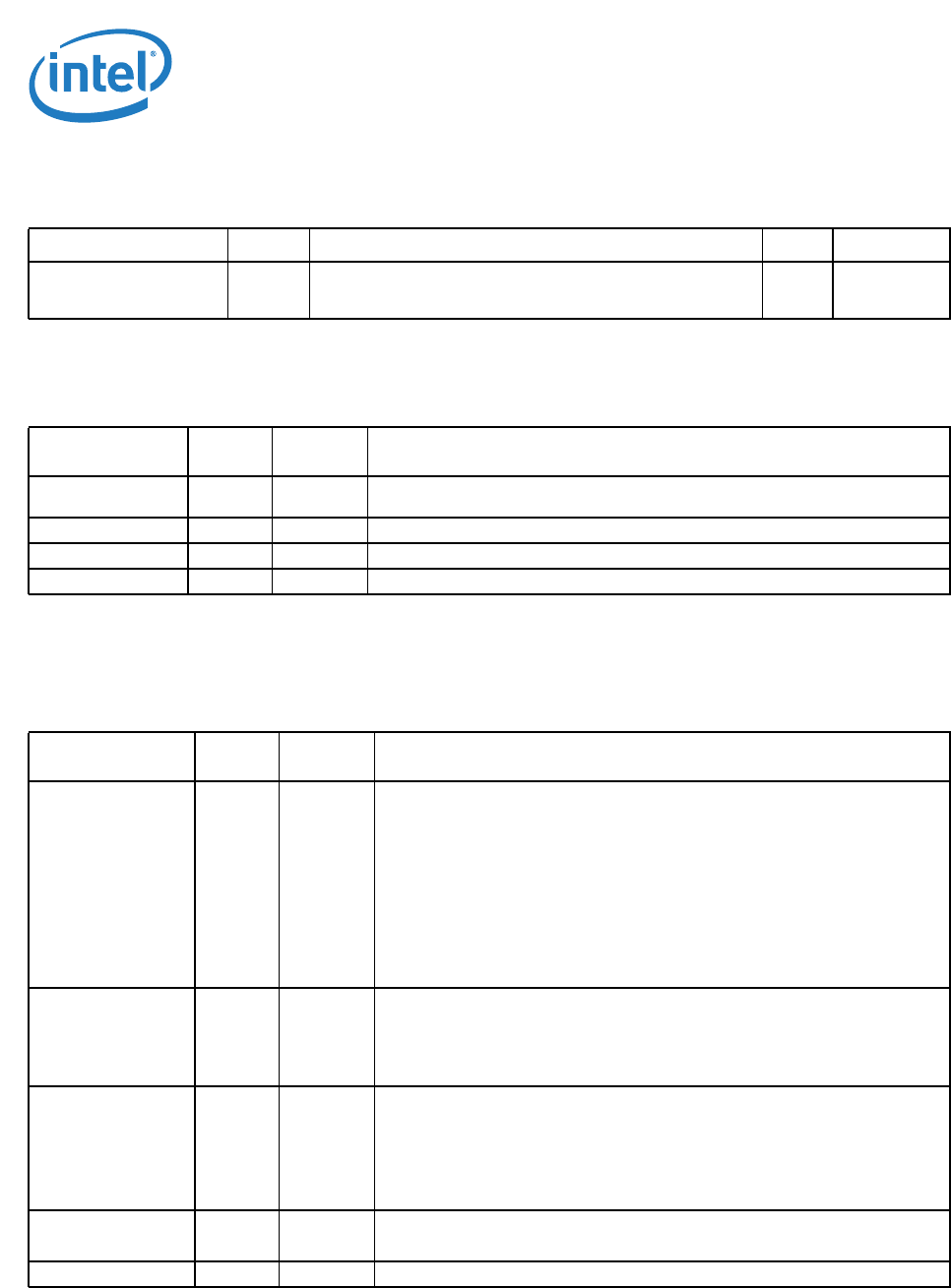

14.3.8.23 Page Select Core Register - (31d; WO)

14.3.9 SERDES ANA - SERDESCTL (00024h; R/W)

14.3.10 Copper/Fiber Switch Control - CONNSW

(00034h; R/W)

Field Bit(s) Description Mode Default

PAGE_SEL 15:0 This register is used to swap out the Base Page containing the

IEEE registers for Intel reserved test and debug pages

residing within the Extended Address space.

WO 0b

Field Bit(s)

Initial

Value

Description

Done Indication 31 1b When a write operation completes, this bit is set to 1b indicating that new data

can be written. This bit is over written to 0b by new data.

Reserved 30:16 0b Reserved.

Address 15:8 0b Address to SerDes.

Data 7:0 0b Data to SerDes.

Field Bit(s)

Initial

Value

Description

AUTOSENSE_EN 0 0B Auto Sense Enable

When set, the auto sense mode is active. In this mode the non-active link is

sensed by hardware as follows

PHY Sensing: The electrical idle detector of the receiver of the PHY is activated

while in SerDes or SGMII mode.

SerDes sensing: The electrical idle detector of the receiver of the SerDes is

activated while in internal PHY mode, assuming the ENRGSRC bit is cleared

If energy is detected in the non active media, the OMED bit in the ICR register

is set and this bit is cleared. This includes the case where energy was present at

the non-active media when this bit is being set.

AUTOSENSE_

CONF

1 0b Auto Sense Config Mode

This bit should be set during the configuration of the PHY/SerDes towards the

activation of the auto-sense mode. While this bit is set, the PHY/SerDes is

active even though the active link is set to SerDes or SGMII/PHY. Energy

detection while this bit is set will not be reflected to the OMED interrupt.

ENRGSRC 2 0b

1

SerDes Energy Detect Source

If set, the OMED interrupt cause is set after asserting the external signal detect

pin. If cleared, the OMED interrupt cause is set after exiting from electrical idle

of the SerDes receiver.

This bit also defines the source of the signal detect indication used to set link up

while is SerDes mode.

Reserved 3 0b Reserved

Must be set to 0b.

Reserved 8:4 0h Reserved