Advanced Receive Descriptors — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 115

5.3.4.10 Packet Buffer (Number of Bytes Exists in the Host

Packet Buffer)

The length covers the data written to a receive buffer including CRC bytes (if any). Software must read

multiple descriptors to determine the complete length for packets that span multiple receive buffers. If

SRRCTL.DESC_TYPE = 4 (advanced descriptor header replication large packet only) and the total

packet length is smaller than the size of the header buffer (no replication is done), this field will still

reflect the size of the packet, although no data is written to the packet buffer. Otherwise, if the buffer is

not split because the header is bigger than the allocated header buffer, this field will reflect the size of

the data written to the first packet buffer (header + data).

TCPE 9 TCP/UDP Checksum Error.

Indicates that the TCP or UDP checksum is incorrect. If TCP/UDP checksum offload is disabled by

RXCSUM.TUOFL, this bit is 0b.

The IP and TCP checksum error bits are valid only when the IPv4 or TCP/UDP checksum(s) is

performed on the received packet as indicated via IPCS and TCPCS. These, along with the other error

bits, are valid only when the EOP and DD bits are set in the descriptor.

Note: Receive checksum errors have no effect on packet filtering.

If receive checksum offloading is disabled (RXCSUM.IPOFL & RXCSUM.TUOFL), then the IPE and

TCPE bits are 0b.

In 10/100/1000BASE-T mode, the RXE bit indicates that a data error occurred during the packet

reception that has been detected by the PHY. This generally corresponds to signal errors occurring

during the packet reception. This bit is valid only when the EOP and DD bits are set and is not set in

descriptors unless RCTL.SBP is set.

CRC errors and alignment errors are both indicated via the CE bit. Software might distinguish

between these errors by monitoring the respective statistics registers.

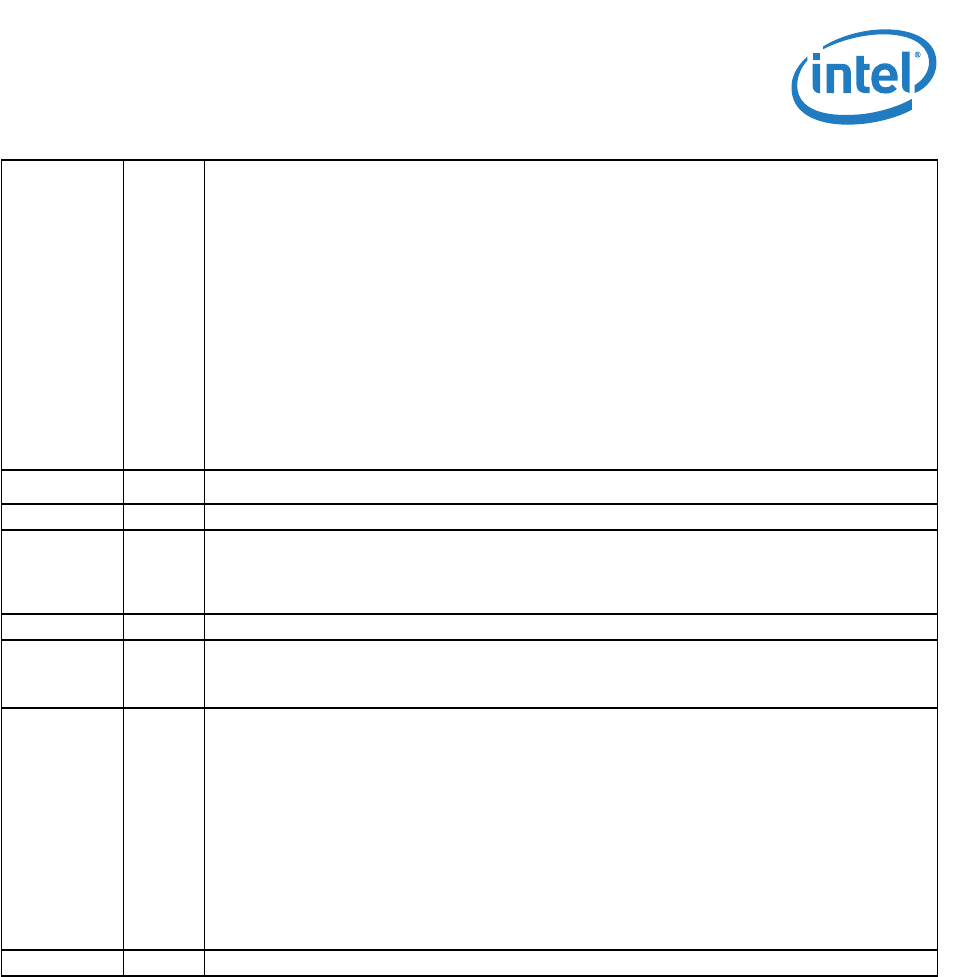

Field Bit(s) Description

Reserved 8 Reserved.

LE 7 Length Error

Indicates packets with length error. For example, indicates valid packets (no CRC error) with a type/

length field with a value lower or equal 1500 greater than the L2 payload size. Packets with length

error are forwarded to the host only if RFCTL.LEF bit is set or RFCTL.SBP bit is set.

SE 5 Symbol Error.

CE 4 CRC Error or Alignment Error.

Indicates an Ethernet CRC error was detected. This bit is valid only when the EOP and DD bits are set

and is not set in descriptors unless RCTL.SBP is set.

HBO 3 Header Buffer Overflow (header is bigger than the header buffer).

Note: This bit is relevant only if the SPH bit is set.

In both Header Replication modes, HBO is set if the header size (as calculated by the hardware) is

bigger than the allocated buffer size (PSRCTL.BSIZEHEADER) but the replication will still take place

up to the header buffer size. HW will set this bit in order to indicate to the SW it needs to allocate

bigger buffers for the headers.

In Header Split mode, when SRRCTL[n] BSIZEHEADER is smaller than HDR_BUF_LEN, then HBO is

set to 1b. In this case, the header is not split. Instead, the header resides within the Host Packet

Buffer. The HDR_BUF_LEN field is still valid and equal to the calculated size of the header. However,

the header is not copied into the header buffer.

Note: Most error information appears only when the Store Bad Buffers bit (RCTL.SBP) is set and a

bad packet is received.

Reserved 2:0 Reserved.