Intel

®

82575EB Gigabit Ethernet Controller — NC-SI Configuration Structure

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

86 January 2011

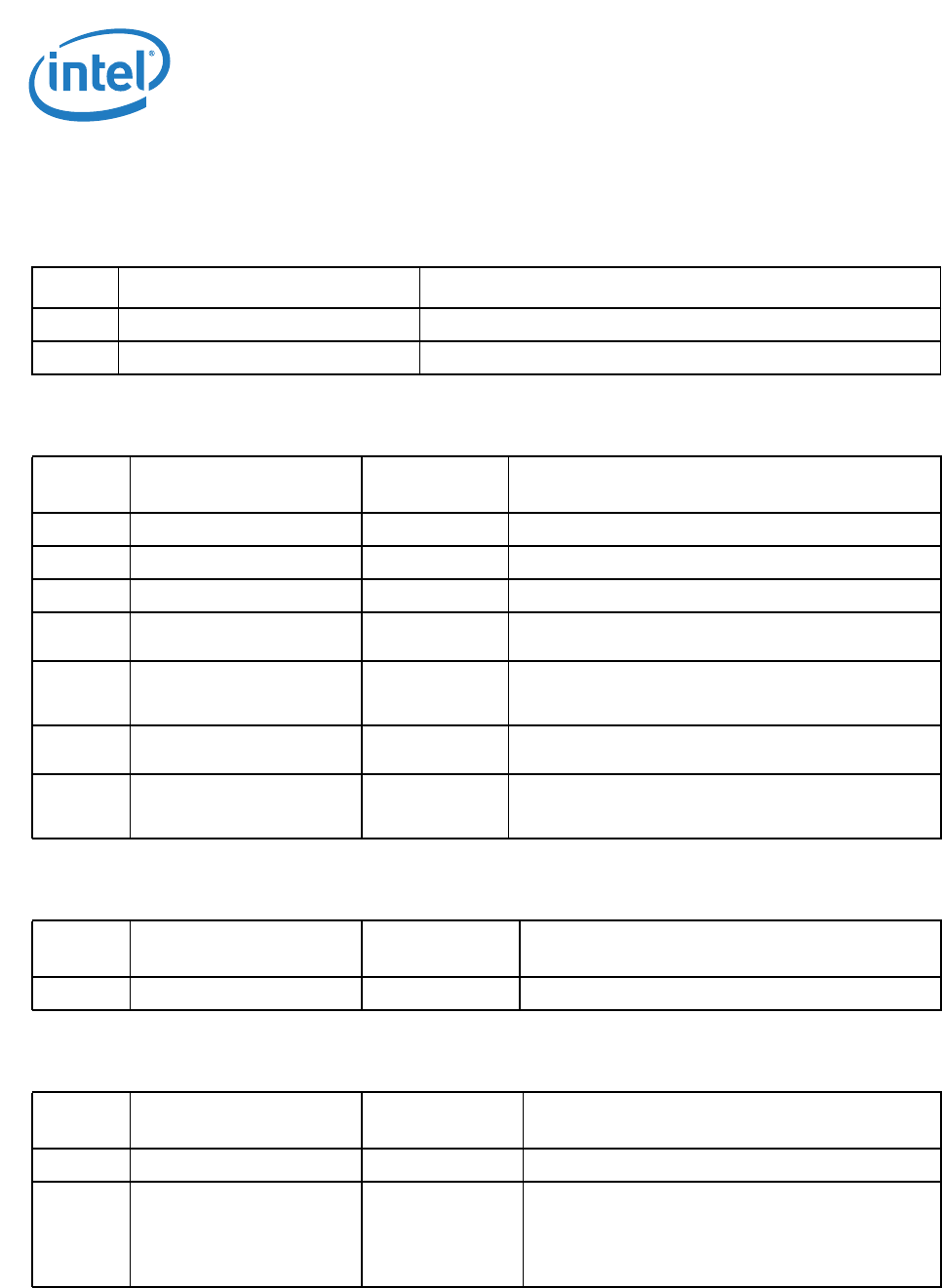

4.6.4 NC-SI Configuration Structure

4.6.4.1 Section Header - (0ffset 0h)

4.6.4.2 Rx Mode Control1 (RR_CTRL[15:0]) (Offset 01h)

4.6.4.3 Rx Mode Control2 (RR_CTRL[31:16]) (Offset 02h)

4.6.4.4 Tx Mode Control1 (RT_CTRL[15:0]) (Offset 03h)

Bit Name Description

15:8 Block CRC8

7:0 Block Length

Bit Name

HDW Default

0Ch

Description

15:8 Reserved 0 Should be 0b.

7:5 Reserved 0 Reserved.

4 False Carrier Enable 0b

3 NC-SI Speed 1b When set, the NC-SI MAC speed is 100 Mb/s. When reset,

NC-SI MAC speed is 10 Mb/s.

2 Receive Without Leading

Zeros

0b If set, packets without leading zeros (such as /J/K/

symbols) between TXEN assertion and TXD first preamble

byte can be received.

1 Clear Rx Error 1b Should be set when the Rx path is stuck because of an

overflow condition.

0 NC-SI Loopback Enable 0b When set, Enables NC-SI Tx to Rx loop. All data that is

transmitted from NC-SI is returned to it. No data is

actually transmitted from the NC-SI.

Bit Name

HDW Default

00h

Description

15:0 Reserved 00h Should be 0b.

Bit Name

HDW Default

00h

Description

15:3 Reserved 0 Should be 0b.

2 Transmit With Leading Zeros 0b When set, send leading zeros (such as /J/K/ symbols)

from CRS_DV assertion to start of preamble (PHY

Mode).

When deasserted, doesn’t send leading zeros (MAC

mode).