Intel

®

82575EB Gigabit Ethernet Controller — Flash Opcode - FLASHOP (0103Ch; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

334 January 2011

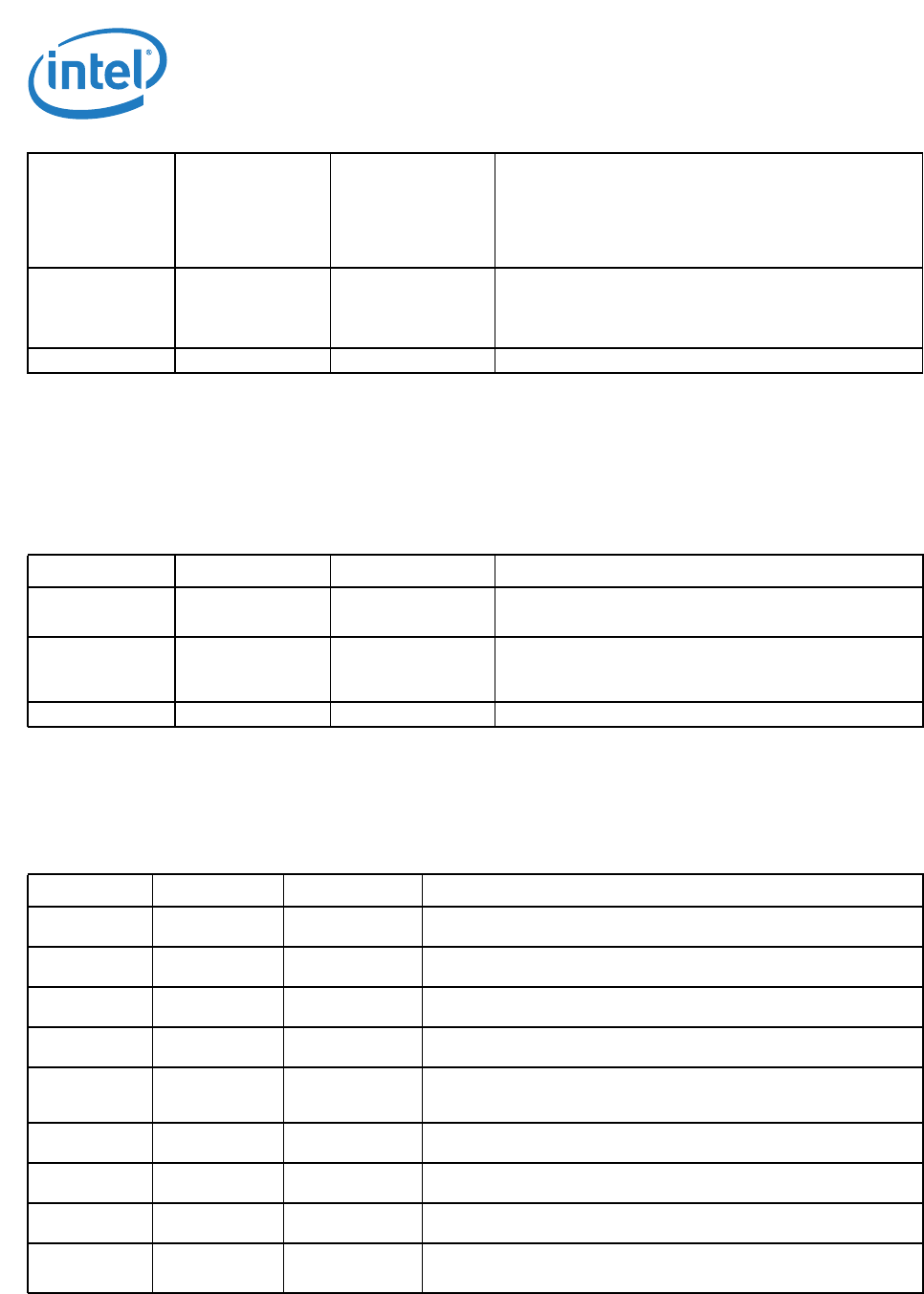

14.3.22 Flash Opcode - FLASHOP (0103Ch; R/W)

This register enables the host or the firmware to define the op-code used in order to erase a sector of

the flash or the complete flash. This register is reset only at Internal_Power_On_Reset assertion.

Note: The default values fit to Atmel* Serial Flash Memory devices.

14.3.23 EEPROM Diagnostic - EEDIAG (01038h; RO)

This register reflects the values of EEPROM bits influencing the hardware that are not reflected

otherwise.

DATA_OE_N 11 0b I

2

C_DATA_OE_N

While in bit bang mode, controls the direction of the

I2C_DATA pad of this port.

0b = Pad is output.

1b = Pad is input.

DATA_IN (RO) 12 X I

2

C_DATA_IN

Reflects the value of the I2C_DATA pad. While in bit bang

mode and when the DATA_OE_N field is zero, this field

reflects the value set in the DATA_OUT field.

Reserved 31:13 0h Reserved

Field Bit(s) Initial Value Description

DERASE 7:0 0062h Flash Device Erase Instruction

The op-code for the Flash erase instruction.

SERASE 15:8 0052h Flash Block Erase Instruction

The op-code for the Flash block erase instruction. Relevant

only to Flash access by manageability.

Reserved 31:16 0h Reserved

Field Bit(s) Initial Value Description

LAN0 Disable

Strap Behavior

0 0b Reflects the inverse of bit 13 in EEPROM word 20h controlling behavior

of disabling strap for LAN0.

LAN1 Disable

Strap Behavior

1 0b Reflects the inverse of bit 13 in EEPROM word 10h controlling behavior

of disabling strap for LAN1.

LAN1 Disable 2 0b Reflects bit 11 in EEPROM word 10h controlling the disabling of LAN1

as PCIe*.

LAN1 PCI

Disable

3 0b Reflects bit 10 in EEPROM word 10h controlling the disabling of LAN1

as PCIe*.

EEPROM

Deadlock

Release Enable

4 0b Reflects bit 5 in EEPROM word 0Ah controlling the EEPROM deadlock

release enable.

Dynamic IDDQ

Enable

5 0b Reflects bit 15 in EEPROM work 1Eh controlling the dynamic IDDQ

enable.

PLL Shutdown

Enable

6 0b Reflects bit 4 in EEPROM 0Fh controlling the PLL shutdown enable

control.

PLL Switch 7 0b Reflects bit 5 in EEPROM word 21h controlling the timing of the switch

to PLL clock.

NC-SI Clock

Out

8 0b Reflects the NC-SI clock out setting in bit 13 of EEPROM word 15h.