Intel

®

82575EB Gigabit Ethernet Controller — Advanced Receive Descriptors

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

114 January 2011

Note: Unsupported packet types will either have the IXSM bit set, or do not have the IPCS or

TCPCS bits set. Ipv6 packets do not have the IPCS bit set, but might have the TCPCS bit set

if the 82575 recognized the TCP or UDP packet.

5.3.4.9 Extended Errors

VP 3 Packet is 802.1q (matched VET).

The VP field indicates whether the incoming packet's type matches VET and VLAN field is strip (For

example, if the packet is a VLAN (802.1q) type). This bit is set if the packet type matches VET and

CTRL.VME is set.

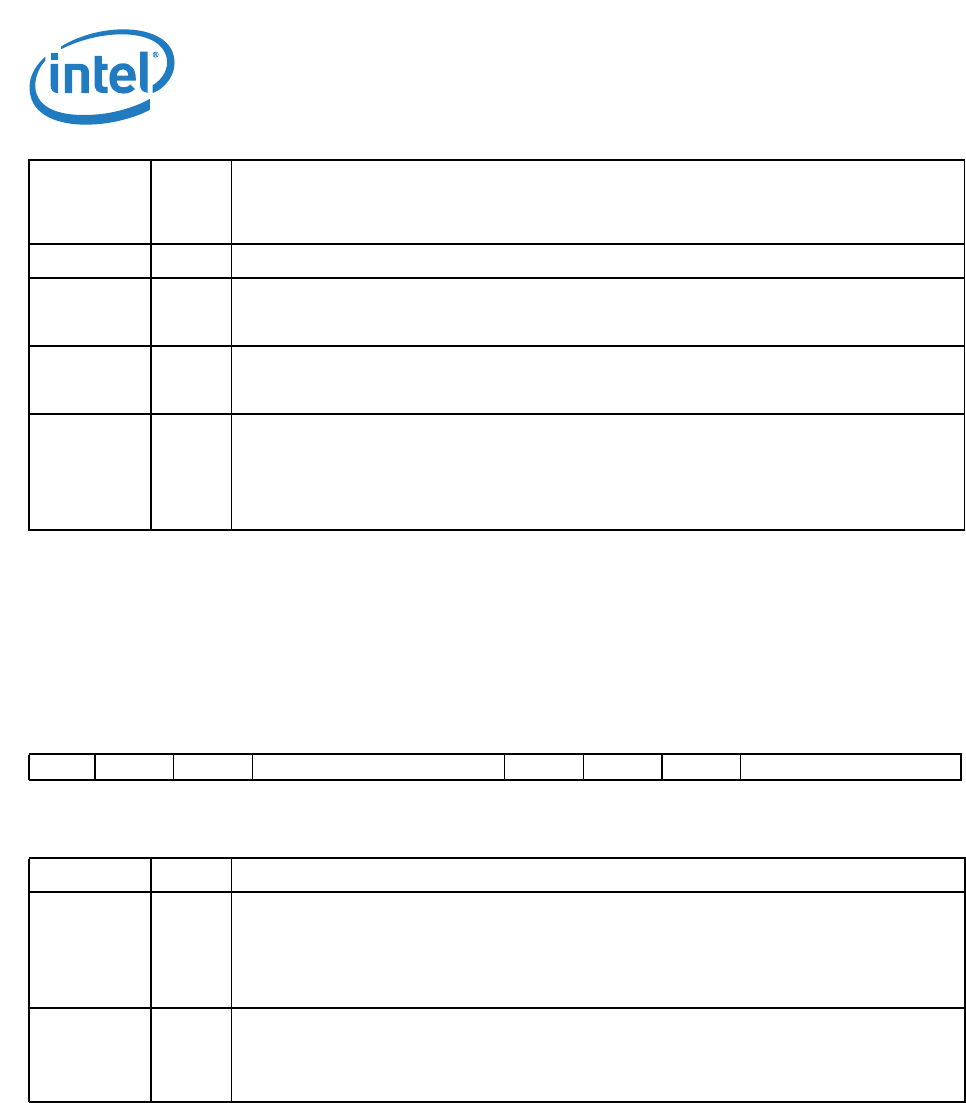

Field Bit(s) Description

IXSM 2 Ignore Checksum Indication.

When set to 1b, hardware does not provide checksum offload. Software device driver should ignore

the IPCS, TCPCS, and UDPCS bits.

EOP 1 End of Packet.

Packets that exceed the receive buffer size span multiple receive buffers. EOP indicates whether this

is the last buffer for an incoming packet.

DD 0 Descriptor Done.

indicates whether hardware is done with the descriptor. When set along with EOP, the received

packet is complete in main memory. Software can determine buffer usage by setting the status byte

to 0b before making the descriptor available to hardware and checking it for non-zero content at a

later time. For multi-descriptor packets, packet status is provided in the final descriptor of the packet

(EOP set). If EOP is not set for a descriptor, only the Address, Length, and DD bits are valid.

11 10 9 8 6 5 4 3 2 0

RXE IPE TCPE Reserved SE CE HBO Reserved

Field Bit(s) Description

RXE 11 Rx Data Error.

Indicates that a data error occurred during the packet reception. A data error refers to the reception

of a /FE/ code from the XGMII interface which eventually causes a CRC error detection (CE bit). This

bit is valid only when the EOP and DD bits are set and is not set in descriptors unless RCTL.SBP is

set. The RXE bit can also be set if a parity error was discovered in the packet buffer while reading

this packet. In this case, RXE might be set even if RCTL.SBP is not set.

IPE 10 IPv4 Checksum Error.

Indicates that the IPv4 header checksum is incorrect. If IPv4 checksum offload is disabled by

RXCSUM.IPOFL, this bit is 0b.