Receive Data FIFO Head Saved Register - RDFHS (02420h; RO) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 433

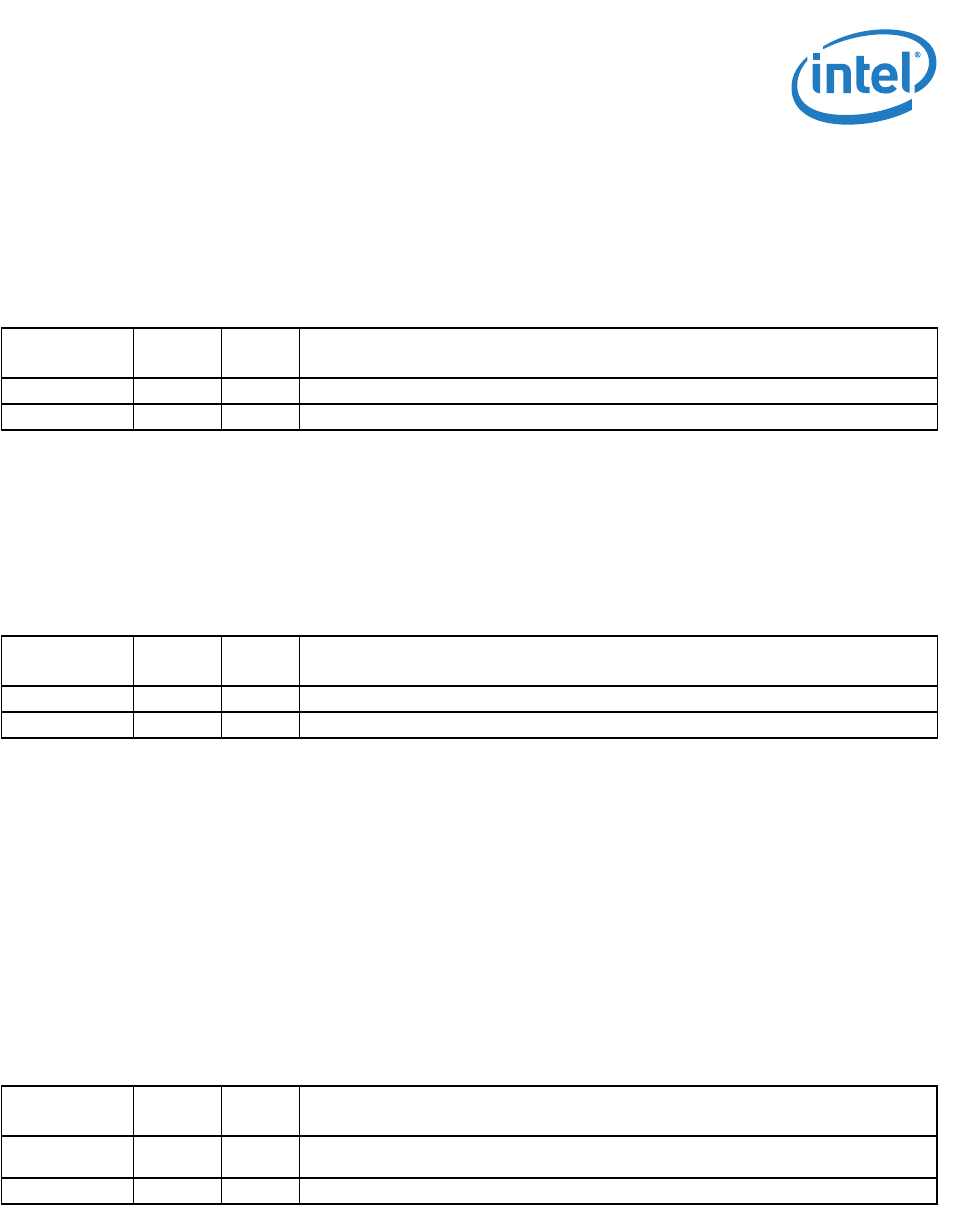

14.10.3 Receive Data FIFO Head Saved Register -

RDFHS (02420h; RO)

This register stores a copy of the Receive Data FIFO Head register in case the internal register needs to

be restored. This register is available for diagnostic purposes only, and should not be written during

normal operation.

14.10.4 Receive Data FIFO Tail Saved Register - RDFTS

(02428h; RO)

This register stores a copy of the Receive Data FIFO Tail register in case the internal register needs to

be restored. This register is available for diagnostic purposes only, and should not be written during

normal operation.

14.10.5 Receive Data FIFO Packet Count - RDFPCQ

(02430h + 4 *n [n=0..3]; RO)

These registers reflect the number of receive packets that are currently in the Receive FIFO that are

dedicated to a given queue.

This counter is reset when the Rx path is enabled by asserting RCTL.RXEN.

• Queue 0 - RDFPCQ0 (02430h; R/W)

• Queue 1 - RDFPCQ1 (02434h; R/W)

• Queue 2 - RDFPCQ2 (02438h; R/W)

• Queue 3 - RDFPCQ3 (0243Ch; R/W)

Field Bit(s)

Initial

Value

Description

FIFO Head 12:0 0b A “saved” value of the Receive FIFO Head pointer.

Reserved 31:13 0b Reads as 0b. Should be written to 0b for future compatibility.

Field Bit(s)

Initial

Value

Description

FIFO Tail 12:0 0b A “saved” value of the Receive FIFO Tail pointer.

Reserved 31:13 0b Reads as 0b. Should be written to 0b for future compatibility.

Field Bit(s)

Initial

Value

Description

RX FIFO

Packet Count

11:0 0b The number of received packets currently in the Rx FIFO.

Reserved 31:12 0b Reads as 0b. Should be written to 0b for future compatibility.