Receive Checksum Control - RXCSUM (05000h; R/W) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 361

14.3.61 Receive Checksum Control - RXCSUM (05000h;

R/W)

The Receive Checksum Control register controls the receive checksum offloading features of the 82575.

The 82575 supports the offloading of three receive checksum calculations: the Packet Checksum, the IP

Header Checksum, and the TCP/UDP Checksum.

Note: This register should only be initialized (written) when the receiver is not enabled (for

example, only write this register when RCTL.EN = 0b)

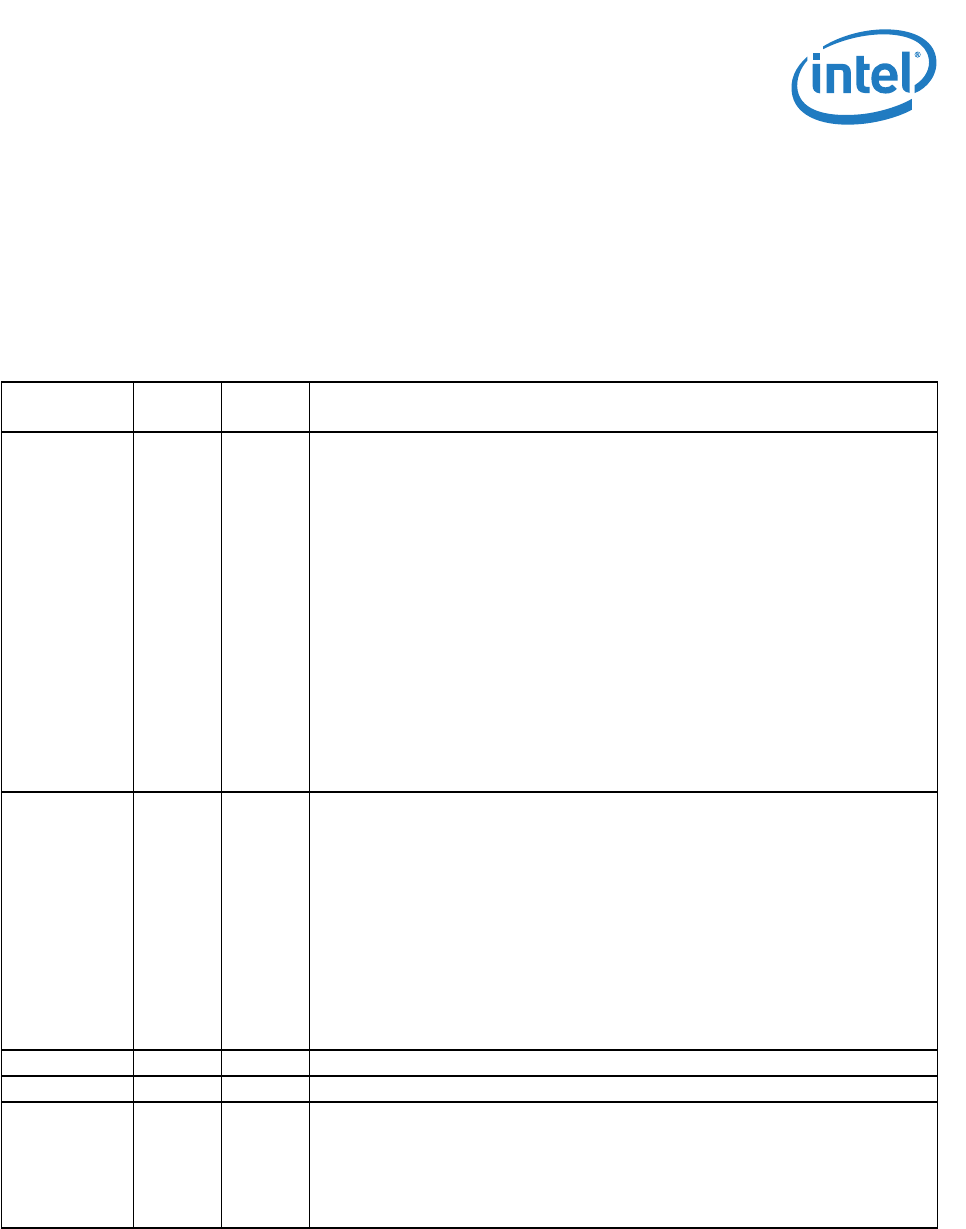

Field Bit(s)

Initial

Value

Description

PCSS 7:0 0h Packet Checksum Start

Controls the packet checksum calculation. The packet checksum shares the same

location as the RSS field and is reported in the receive descriptor when the

RXCSUM.PCSD bit is cleared.

If RXCSUM.IPPCSE cleared (the default value), the checksum calculation that is

reported in the Rx Packet checksum field is the unadjusted 16-bit ones complement of

the packet. The packet checksum starts from the byte indicated by RXCSUM.PCSS (0b

corresponds to the first byte of the packet), after VLAN stripping if enabled by the

CTRL.VME. For example, for an Ethernet II frame encapsulated as an 802.3ac VLAN

packet and with RXCSUM.PCSS set to 14, the packet checksum would include the

entire encapsulated frame, excluding the 14-byte Ethernet header (DA, SA, Type/

Length) and the 4-byte VLAN tag. The packet checksum does not include the Ethernet

CRC if the RCTL.SECRC bit is set. Software must make the required offsetting

computation (to back out the bytes that should not have been included and to include

the pseudo-header) prior to comparing the packet checksum against the TCP

checksum stored in the packet checksum is aimed to accelerate checksum calculation

of fragmented UDP packets.

Note: The PCSS value should not exceed a pointer to the IP header start. If

exceeded, the IP header checksum or TCP/UDP checksum will not be calculated

correctly.

IPOFLD 8 1b IP Checksum Off-load Enable

RXCSUM.IPOFLD is used to enable the IP Checksum off-loading feature. If

RXCSUM.IPOFLD is set to 1b, the 82575 calculates the IP checksum and indicates a

pass/fail indication to software via the IP Checksum Error bit (IPE) in the Error field of

the receive descriptor. Similarly, if RXCSUM.TUOFLD is set to 1b, the 82575 calculates

the TCP or UDP checksum and indicates a pass/fail indication to software via the TCP/

UDP Checksum Error bit (TCPE). Similarly, if RFCTL.IPv6_DIS and

RFCTL.IP6Xsum_DIS are cleared to 0b and RXCSUM.TUOFLD is set to 1b, the 82575

calculates the TCP or UDP checksum for IPv6 packets. It then indicates a pass/fail

condition in the TCP/UDP Checksum Error bit (RDESC.TCPE).

This applies to checksum offloading only. Supported frame types:

Ethernet II

Ethernet SNAP

TUOFLD 9 1b TCP/UDP Checksum Off-load Enable

Reserved 10 0b Reserved

CRCOFL 11 0b CRC32 Offload Enable

Enables the CRC32 checksum off-loading feature. If RXCSUM.CRCOFL is set to 1b, the

82575 calculates the CRC32 checksum and indicates a pass/fail indication to software

via the CRC32 Checksum Valid bit (CRCV) in the Extended Status field of the receive

descriptor.

In non I/OAT, this bit is read only as 0b.