Intel

®

82575EB Gigabit Ethernet Controller — SerDes/SGMII Code Violation Packet Count - SCVPC

(04228h; R/WS)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

432 January 2011

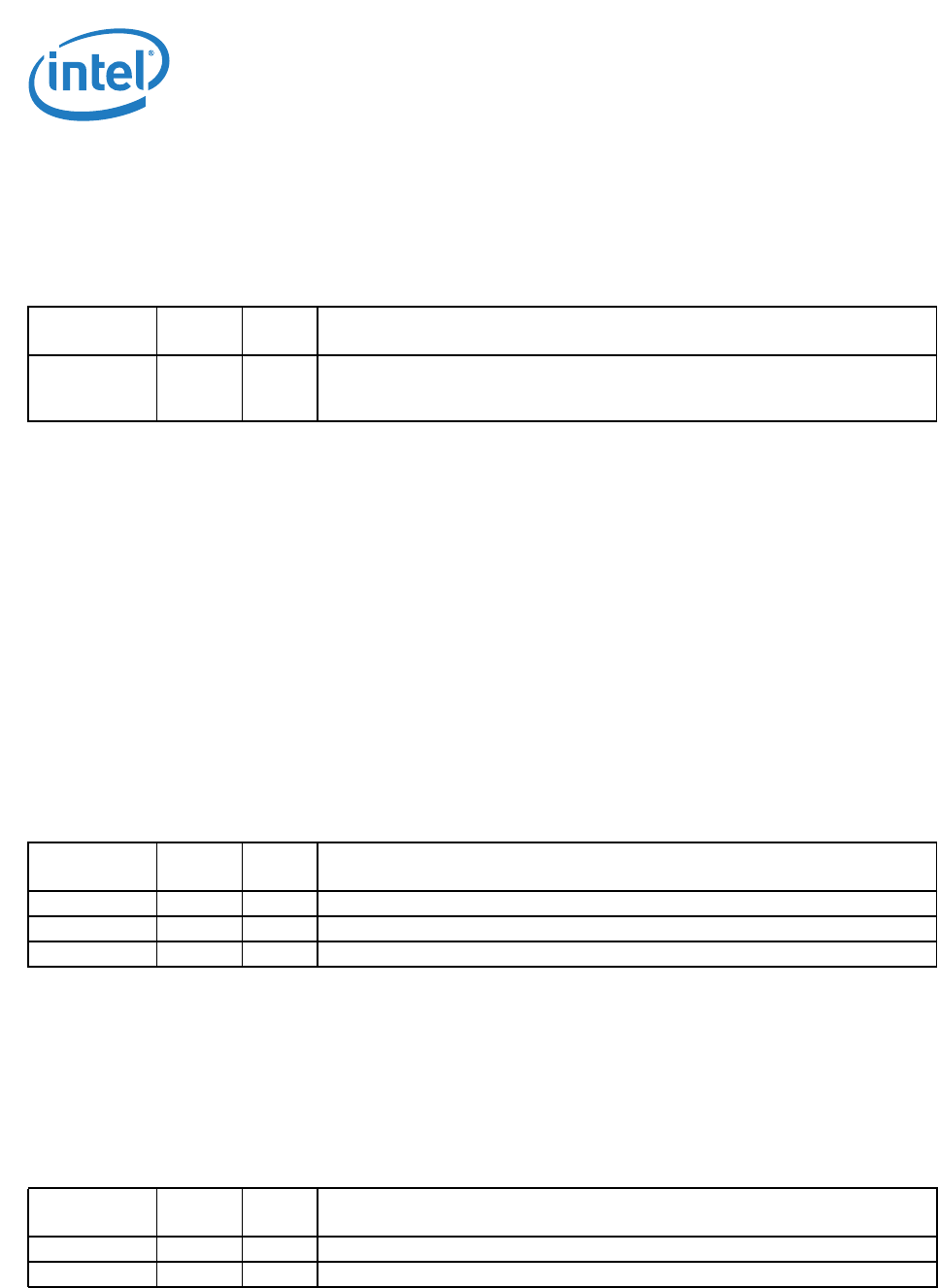

14.9.57 SerDes/SGMII Code Violation Packet Count -

SCVPC (04228h; R/WS)

This register contains the number of code violation packets received on a particular GbE port. Code

violation is defined as a invalid received code in the middle of a packet.

14.10 Diagnostics Registers

The 82575 contains several diagnostic registers. These registers enable software to directly access the

contents of the 82575’s internal Packet Buffer Memory (PBM), also referred to as FIFO space. These

registers also give software visibility into what locations in the PBM that the hardware currently

considers to be the “head” and “tail” for both transmit and receive operations.

14.10.1 Receive Data FIFO Head Register - RDFH

(02410h; RO)

This register stores the head of the on–chip receive data FIFO. Since the internal FIFO is organized in

units of 64-bit words, this field contains the 64-bit offset of the current Receive FIFO Head. So a value

of “8h” in this register corresponds to an offset of 8 Qwords into the Receive FIFO space. This register is

available for diagnostic purposes only, and should not be written during normal operation.

14.10.2 Receive Data FIFO Tail Register - RDFT

(02418h; RO)

This register stores the tail of the on–chip receive data FIFO. Since the internal FIFO is organized in

units of 64-bit words, this field contains the 64-bit offset of the current Receive FIFO Tail. So a value of

“8h” in this register corresponds to an offset of eight Qwords or into the Receive FIFO space. This

register is available for diagnostic purposes only, and should not be written during normal operation.

Field Bit(s)

Initial

Value

Description

CODEVIO 31:0 X Code Violation Packet Count

At any point of time this field specifies the number of unknown protocol packets

received. Valid only in SGMII/SerDes mode.

Field Bit(s)

Initial

Value

Description

FIFO Head 12:0 0b Receive FIFO Head pointer.

Reserved 30:13 0b Reads as 0b. Should be written to 0b for future compatibility.

FIFO Full 31 0b Rx Memory Full Signal

Field Bit(s)

Initial

Value

Description

FIFO Tail 12:0 0b Receive FIFO Tail pointer.

Reserved 31:13 0b Reads as 0b. Should be written to 0b for future compatibility.