Tx Descriptor Handler ECC Status - TDHESTS (0246Ch; R/W) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 441

14.10.22 Tx Descriptor Handler ECC Status - TDHESTS

(0246Ch; R/W)

14.11 Packet Generator Registers

This section contains detailed descriptions for those registers associated with the 82575’s packet

generator capabilities.

14.11.1 Packet Generator Destination Address Low -

PGDAL (04280h; R/W)

14.11.2 Packet Generator Destination Address High -

PGDAH (04284h; R/W)

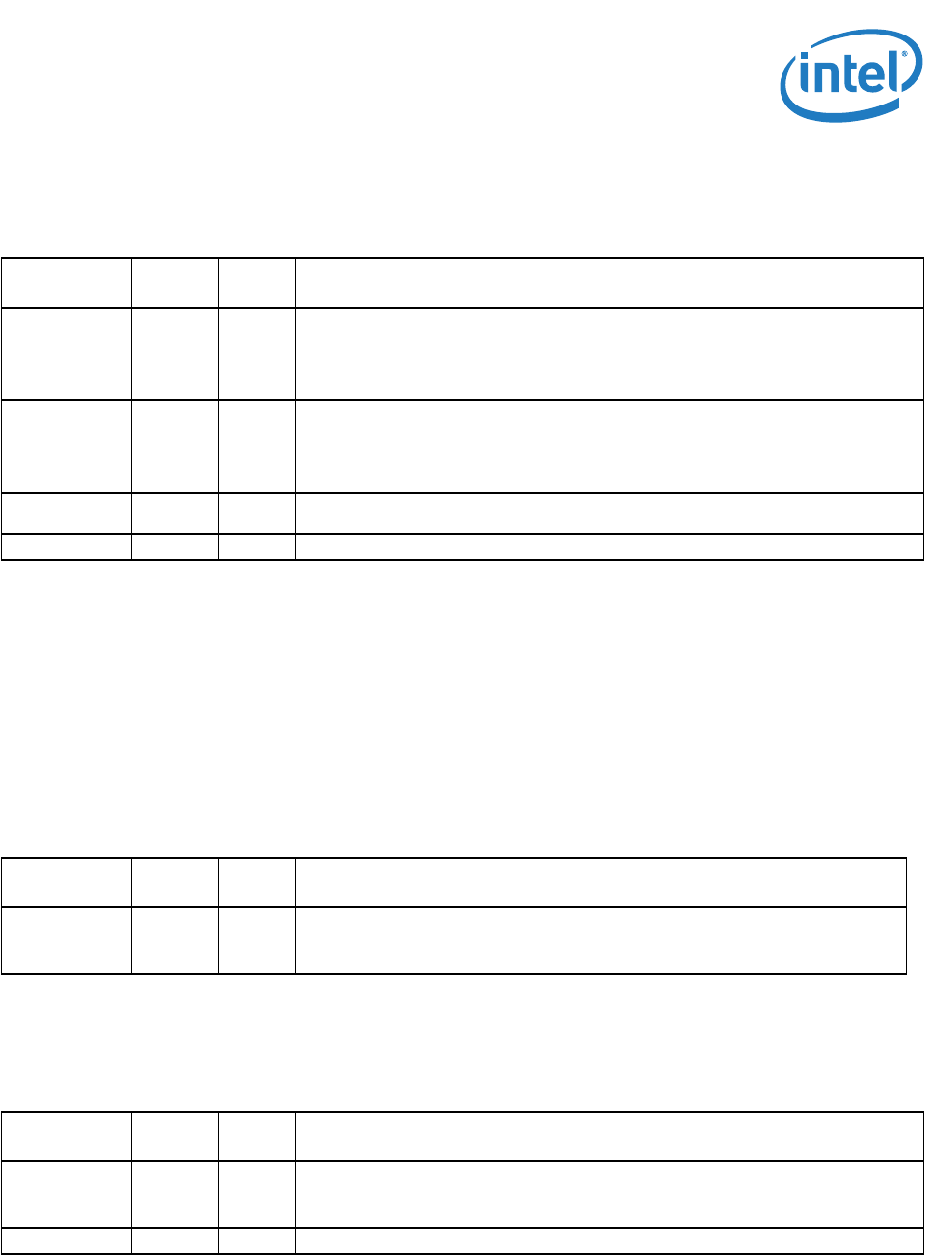

Field Bit(s)

Initial

Value

Description

Corr_err_cnt 7:0 0h Correctable Error Count

This counter is increment every time a correctable error is detected in the Tx descriptor

handler memory; the counter stops after reaching FFh.

These bits are cleared by reads.

Uncorr_err_cnt 15:8 0h Uncorrectable Error Count

This counter is increment every time a correctable error is detected in the Tx descriptor

handler memory; the counter stops after reaching FFh.

These bits are cleared by reads.

TDHECC

Enable

16 1b Tx Descriptor Handler ECC Enable

Reserved 31:17 0b Reserved

Field Bit(s)

Initial

Value

Description

DA 31:0 0h Packet Generator Destination Address Low

The lower 32 bits of the 48 bit Ethernet destination address used for packets sent by

the packets generator.

Field Bit(s)

Initial

Value

Description

DA 15:0 0h Packet Generator Destination Address High

The higher 16 bits of the 48-bit Ethernet destination address used for packets sent by

the packets generator.

Reserved 31:16 0h Reserved