Completion Timeout Mechanism — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 181

IDs are as in data movement engine 1 mode. When in data movement engine 2 mode,

messages and MSI/MSI-X write requests are sent with a hint tag of 1Fh.

6.3.2 Completion Timeout Mechanism

The completion timeout mechanism is activated for each request that requires one or more completions

when the request is transmitted. Revision 1.1 of the PCI specification requires:

• Completion Timeout timer should not expire in less than 10 ms.

• Completion Timeout timer must expire if a request is not completed in 50 ms.

However, some platforms experience completion latencies that are longer than 50 ms, in some cases up

to seconds. The 82575 provides a programmable range for the completion timeout as well as the ability

to disable the completion timeout altogether. The new capability structure is assigned a PCIe* capability

structure version of 2h.

The 82575 controls the following aspects of completion timeout:

• Disabling or enabling completion timeout

• Disabling or enabling resending a request on completion timeout

• A programmable range of timeout values

Programming the behavior of completion timeout is done differently whether capability structure

version 1h is enabled or capability structure version 2h. Table 57 lists the behavior for both cases.

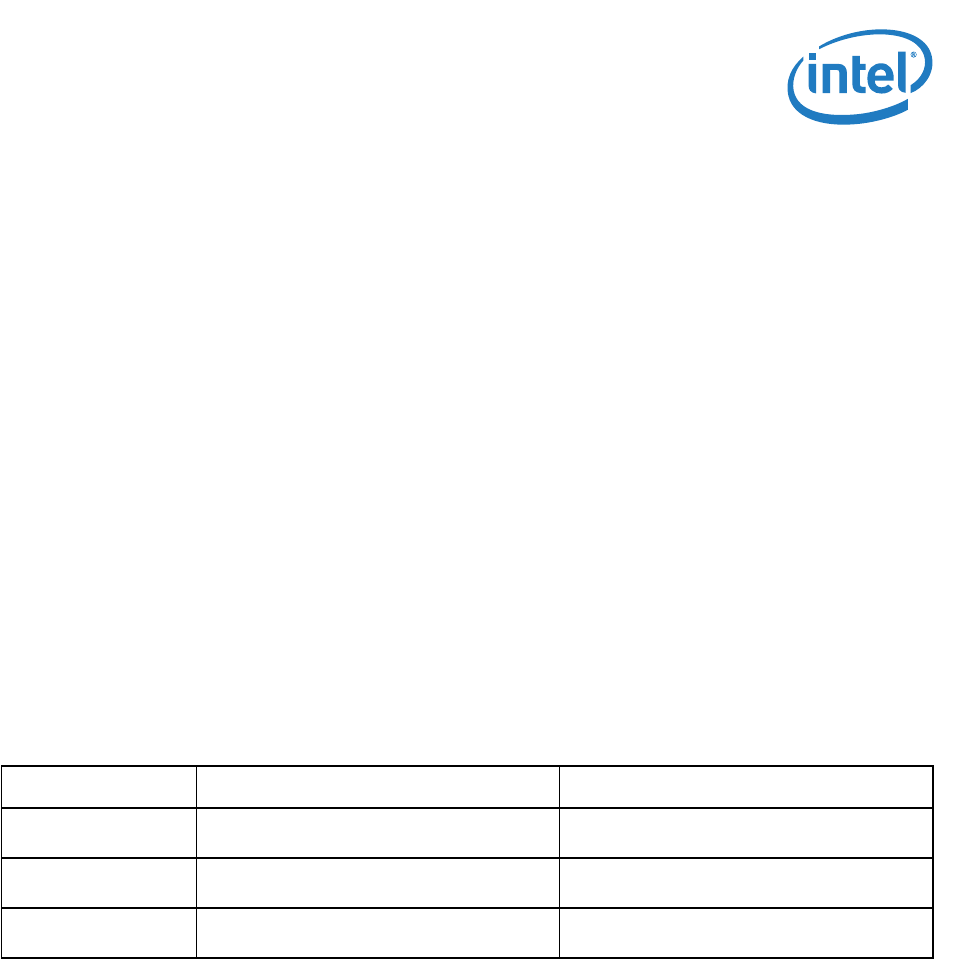

Table 57. Completion Timeout Programming

Completion Timeout Enable:

• Version = 1h- Loaded from the Completion Timeout Disable bit in the EEPROM into the

Completion_Timeout_Disable bit in the PCIe* Control register (GCR). The default is completion

timeout enabled.

• Version = 2h - Programmed through PCI configuration. Visible through the

Completion_Timeout_Disable bit in the PCIe* Control register (GCR). The default is completion

timeout enabled.

Resend Request Enable:

• The Completion Timeout Resend EEPROM bit, loaded in the Completion_Timeout_Resend bit in the

PCIe* Control register (GCR), enables resending the request (applies only when completion timeout

is enabled). The default is to resend a request that timed out.

Completion Timeout Period:

• Version = 1h.- Loaded from the Completion Timeout Value field in the EEPROM to the _

Completion_Timeout_Value bits in the PCIe* Control register (GCR).

Capability Capability Structure Version = 1h Capability Structure Version = 2h

Completion timeout

enabling

Loaded from EEPROM into CSR bit Controlled through PCI configuration. Visible

through read-only CSR bit

Resend request

enable

Loaded from EEPROM into CSR bit Loaded from EEPROM into read-only CSR bit

Completion Timeout

period

Loaded from EEPROM into CSR bit Controlled through PCI configuration. Visible

through read-only CSR bit