Intel

®

82575EB Gigabit Ethernet Controller — Clearing Interrupt Causes

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

168 January 2011

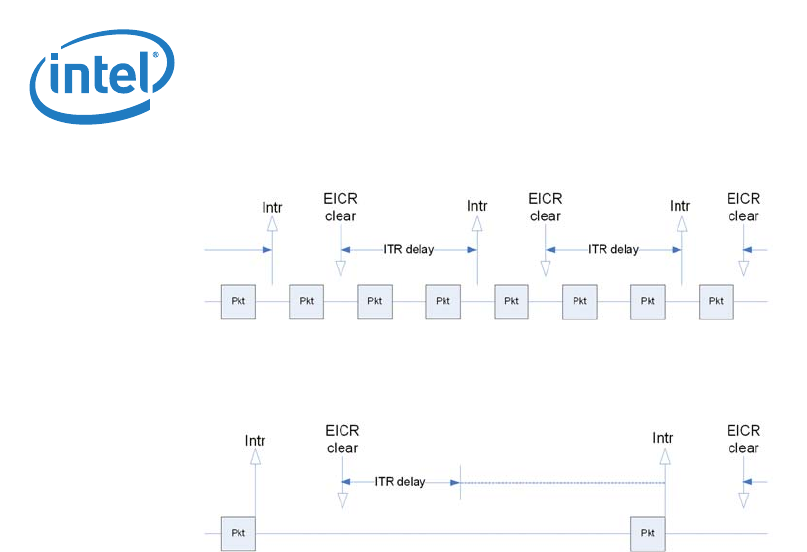

Figure 21. Case A: Heavy Load, Interrupts Moderated

Figure 22. Case B: Light Load, Interrupts Immediately on Packet Receive

5.15 Clearing Interrupt Causes

The 82575 has three available methods for clearing the EICR bits: auto-clear, clear-on-write, and clear-

on-read. Note that ICR bits can only be cleared with clear-on-write or clear-on-read.

5.15.1 Auto-Clear

In systems that support MSI-X, the interrupt vector enables the interrupt service routine to know the

interrupt cause without reading EICR. With interrupt moderation active, software loads from spurious

interrupts is minimized. In this case, the software overhead of a I/O read or write can be avoided by

setting appropriate EICR bits to auto-clear mode by setting the corresponding bits in the EIAC.

When auto-clear is enabled for a interrupt cause, the EICR bit is set when a cause event occurs. When

the EITR counter reaches zero, the MSI-X message is sent on to the PCIe* interface. Afterwards, the

EICR bit is cleared and enabled to be set by a new cause event. The vector in the MSI-X message

signals software the cause of the interrupt to be serviced.

It is possible that in the time after the EICR bit is cleared and the interrupt service routine services the

cause, for example checking the transmit and receive queues, that another cause event occurs that is

then serviced by this ISR call, yet the EICR bit remains set. This results in a spurious interrupt.

Software can detect this case, for example if there are no entries that require service in the transmit

and receive queues, and exit knowing that the interrupt has been automatically cleared. The use of

interrupt moderations through the EITR register limits the extra software overhead that can be caused

by these spurious interrupts.