Intel

®

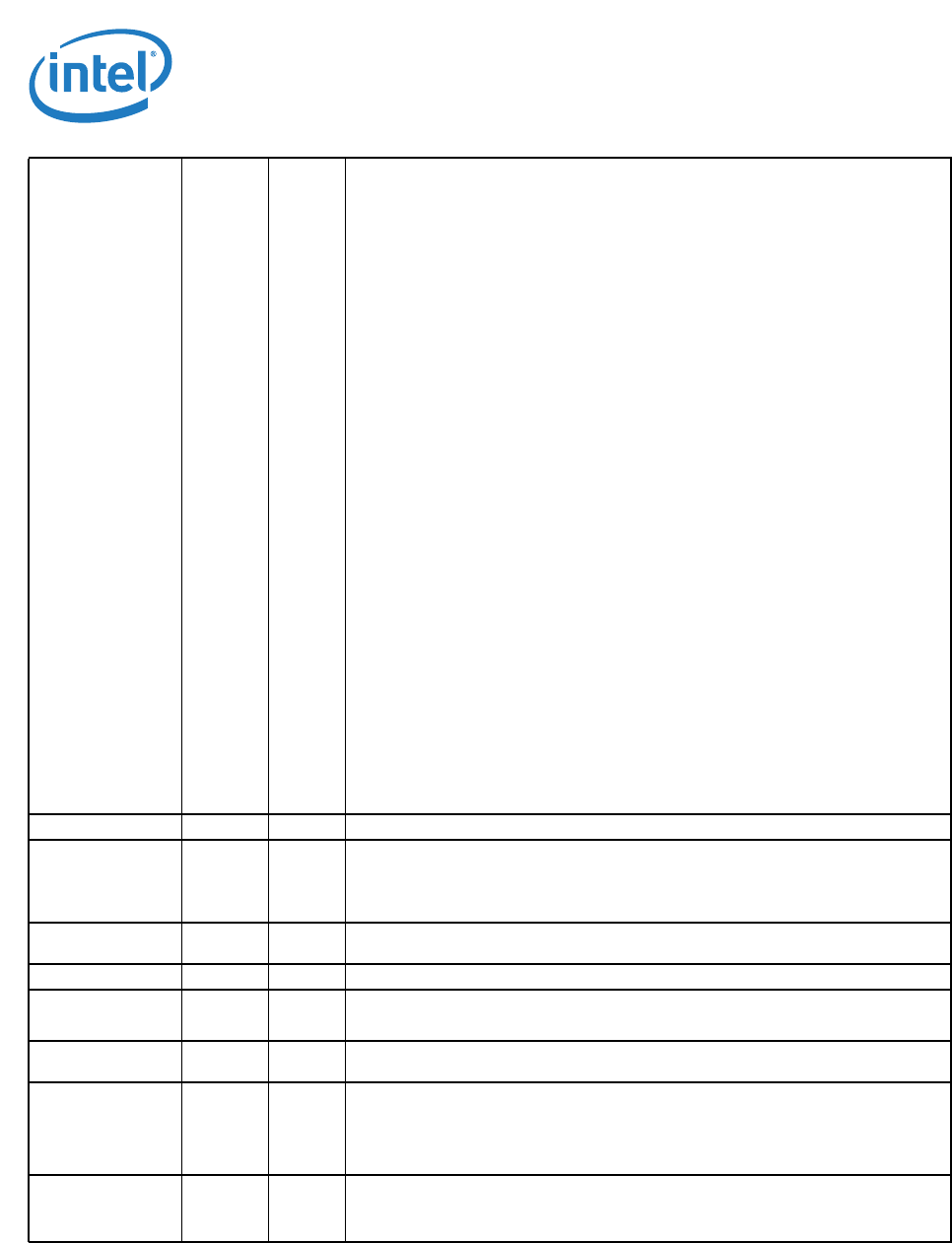

82575EB Gigabit Ethernet Controller — PCIe* Control - GCR (05B00h; R)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

402 January 2011

Completion_

Timeout_Value

(RO or RW1)

15:12 0h Indicates the selected value for completion timeout (after an

Internal_Power_On_Reset).

Decoding of this field depends on the PCIe* capability version:

Capability version = 1 (bits 13:12):

00b = 50 s to 10 ms (default)

01b = 10 ms to 200 ms

10b = 200 ms to 4 s

11b = 4 s to 64 s

Bits 15:14 are reserved

Capability version = 2:

0000b = 50 s to 50 ms

0001b = 50 s to 100 s

0010b = 1 ms to 10 ms

0011b = Reserved

0100b = Reserved

0101b = 16 ms to 55 ms

0110b = 65 ms to 210 ms

0111b = Reserved

1000b = Reserved

1001b = 260 ms to 900 ms

1010b = 1 s to 3.5 s

1011b = Reserved

1100b = Reserved

1101b = 4 s to 13 s

1110b = 17 s to 64 s

1111b = Reserved

Reserved 11:10 00b Reserved

Rx_L0s_Adjustme

nt

9 1b If set, the replay timer always adds the required L0s adjustment (after an

Internal_Power_On_Reset).

When set to 0b, adds it only when Tx L0s are active (after an

Internal_Power_On_Reset).

FW

Self_Test_Enable

8 0b When set, firmware should perform a self test (after an Internal_Power_On_Reset).

Reserved 7:3 0h Reserved

CBDE (RO) 2 0b Data Movement Engine Transfer Enabled

Reflects the transfer enable bit received from the CB_RESPONSE message.

Field Bit(s) Initial

Value

Description

CBA (RO) 1 0b Data Movement Engine Active

This bit is set to 1b following reception of the response VDM sent by the data

movement engine.

If the I/OAT fuse is fused out, then this bit remains reset to 0b.

CBDB (WO) 0 0b Data Movement Engine Doorbell

This bit is used by the software device driver to trigger sending the data movement

engine.