PHY Registers — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 325

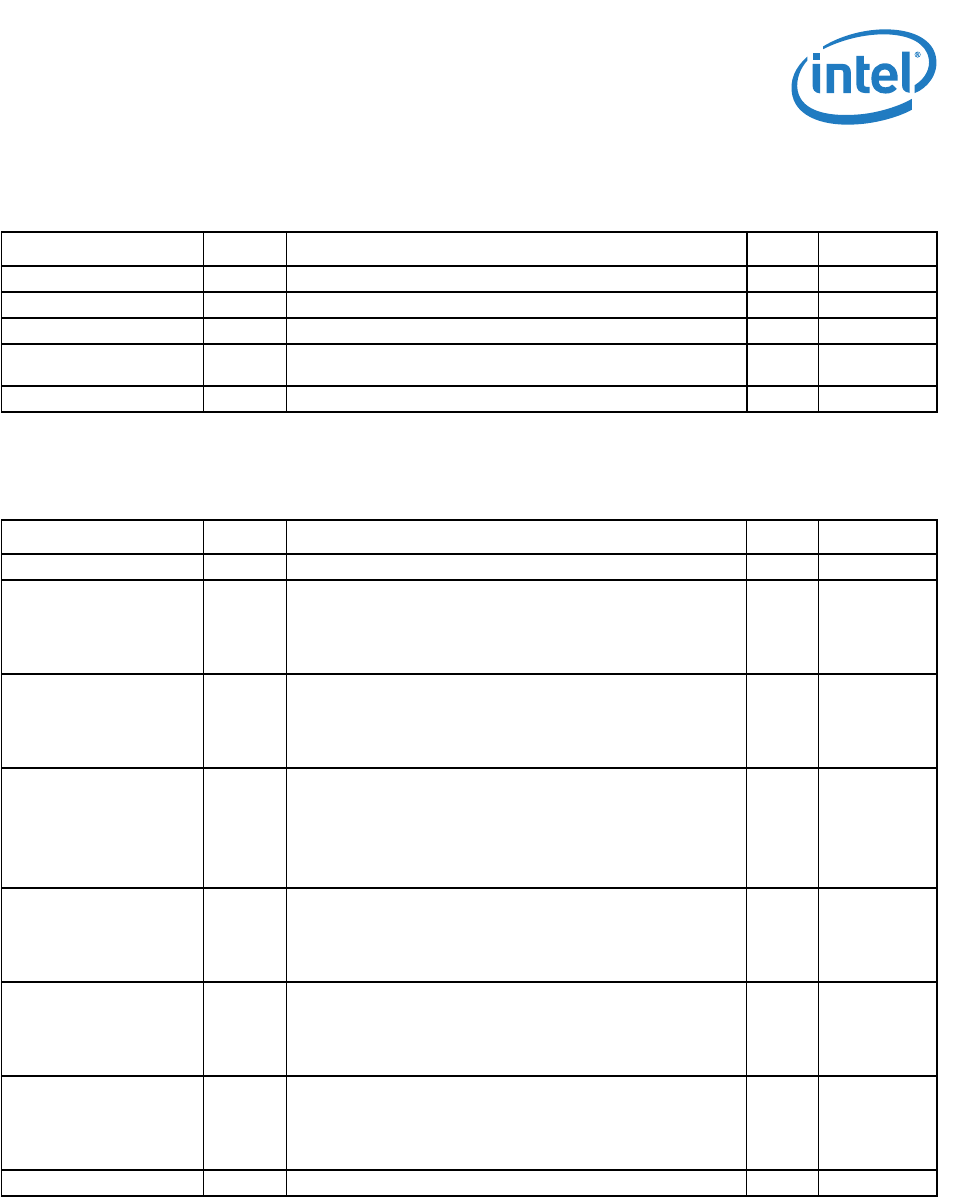

14.3.8.21 Misc Cntrl Register 1 - (27d; R/W)

14.3.8.22 Misc Cntrl Register 2 - (28d; RO)

Note: Bits 13:8 might differ from the corresponding bits in PHY register 04d and 09d due to non-IEEE PHY features (lplu,

an1000_dis, and smart-speed).

Field Bit(s) Description Mode Default

Reserved 15 Ignore this bit. R/W 0b

Reserved 14:9 Always read as 0b. Write to 0b for normal operation. R/W 0b

ss_cfg_cntr 8:6 Smart speed counter configuration: 1-5 (001b:101b). R/W 010b

T10_auto_pol_dis 5 When set, disables the auto-polarity mechanism in the 10

block.

R/W 0b

Reserved 4:0 Always read as 0b. Write to 0b for normal operation. R/W 0b

Field Bit(s) Description Mode Default

Reserved 15:14 Always read as 0b. Write to 0b for normal operation. R/W 0b

Act_an_adv_gigfdx 13 Indicates the actual AN advertisement of the PHY for 1000

Full-Duplex Capability.

0b = Not 1000 Full Duplex Capable.

1b = 1000 Full Duplex Capable.

RO 0b

Act_an_adv_gighdx 12 Indicates the actual AN advertisement of the PHY for 1000

Half-Duplex Capability.

0b = Not 1000 Half Duplex Capable.

1b = 1000 Half Duplex Capable.

RO 0b

Act_an_adv_100fd 11 Indicates the actual AN advertisement of the PHY for 100 Full-

Duplex Capability.

0b = Not 100 Full Duplex Capable.

1b = 100 Full Duplex Capable.

RO 0b

Act_an_adv_100hd 10 Indicates the actual AN advertisement of the PHY for 100 half-

Duplex Capability.

0b = Not 100 Half Duplex Capable.

1b = 100 Half Duplex Capable.

RO 0b

Act_an_adv_10fdx 9 Indicates the actual AN advertisement of the PHY for 10 Full-

Duplex Capability.

0b = Not 10 Full Duplex Capable.

1b = 10 Full Duplex Capable.

RO 0b

Act_an_adv_10hdx 8 Indicates the actual AN advertisement of the PHY for 10 Half-

Duplex Capability.

0b = Not 10 Half Duplex Capable.

1b = 10 Half Duplex Capable.

RO 0b

Reserved 7:0 Reserved. R/W 0b