VLAN Filter Queue Array 0 - VFQA0 (0B100h + 4*n [n=0…127]; R/W) — Intel

®

82575EB Gigabit

Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 385

14.5.9 VLAN Filter Queue Array 0 - VFQA0 (0B100h +

4*n [n=0…127]; R/W)

This register set classifies receive packets into Rx queues in some schemes for multiple queues. There

is one register per 32 bits of the VLAN Filter Queue Array 0. The VLAN Filter Queue Array 0, together

with the VLAN Filter Queue Array 1, determines the receive queue for received VLAN packets.

• All accesses to this table must be 32 bit.

14.5.10 VLAN Filter Queue Array 1 - VFQA1 (0B200h +

4*n [n=0…127]; R/W)

This register set classifies receive packets into Rx queues in some schemes for multiple queues. There

is one register per 32 bits of the VLAN Filter Queue Array 1. The VLAN Filter Queue Array 1, together

with the VLAN Filter Queue Array 0, determines the receive queue for received VLAN packets. VLAN

Filter Queue Array 1 can alternatively serve as a pool bit in some of the classification schemes.

Note: All accesses to this table must be 32 bit.

14.6 Wakeup Registers

This section contains detailed descriptions for those registers associated with the 82575’s wakeup

capabilities.

14.6.1 Wakeup Control Register - WUC (05800h; R/W)

The PME_En and PME_Status bits of this register are reset when Internal_Power_On_Reset is 0b. When

AUX_PWR = 0b, this register is also reset by de-asserting PE_RST_N and when transitioning from D3 to

D0. The other bits are reset using the standard internal resets.

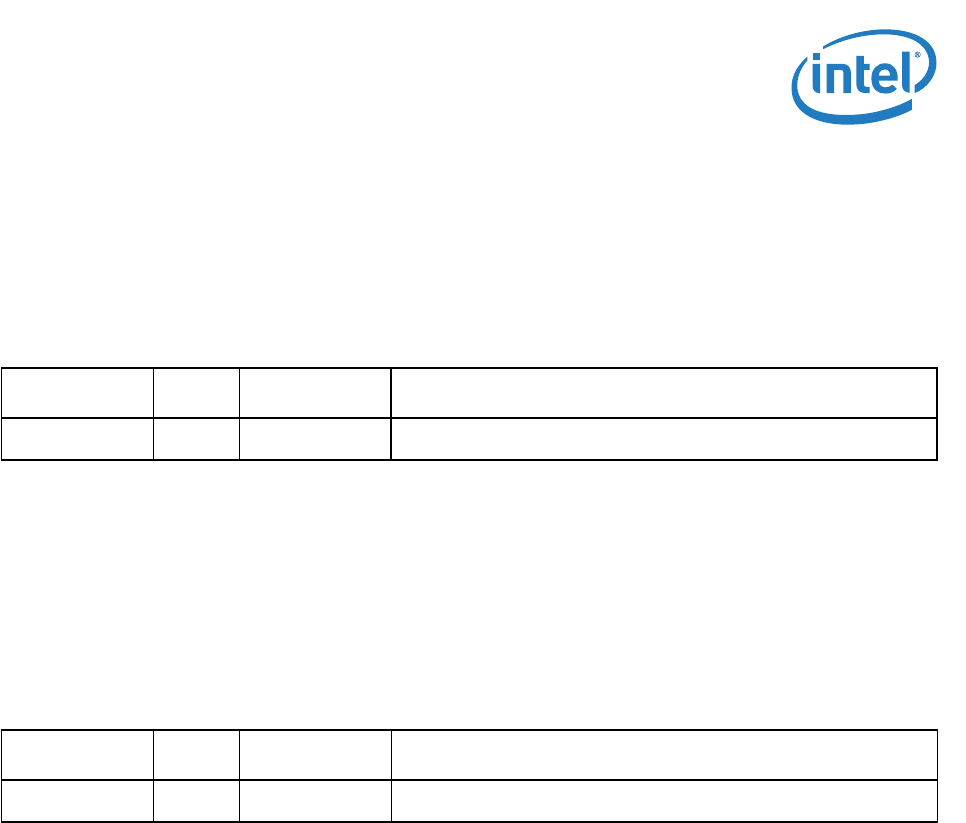

Field Bit(s)

Initial

Value

Description

Bit Vector 31:0 0h Double word wide bit vector specifying 32 bits in the VLAN filter queue

array 0.

Field Bit(s)

Initial

Value

Description

Bit Vector 31:0 0h Double word wide bit vector specifying 32 bits in the VLAN filter queue

array 1.