Intel

®

82575EB Gigabit Ethernet Controller — PHY Registers

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

318 January 2011

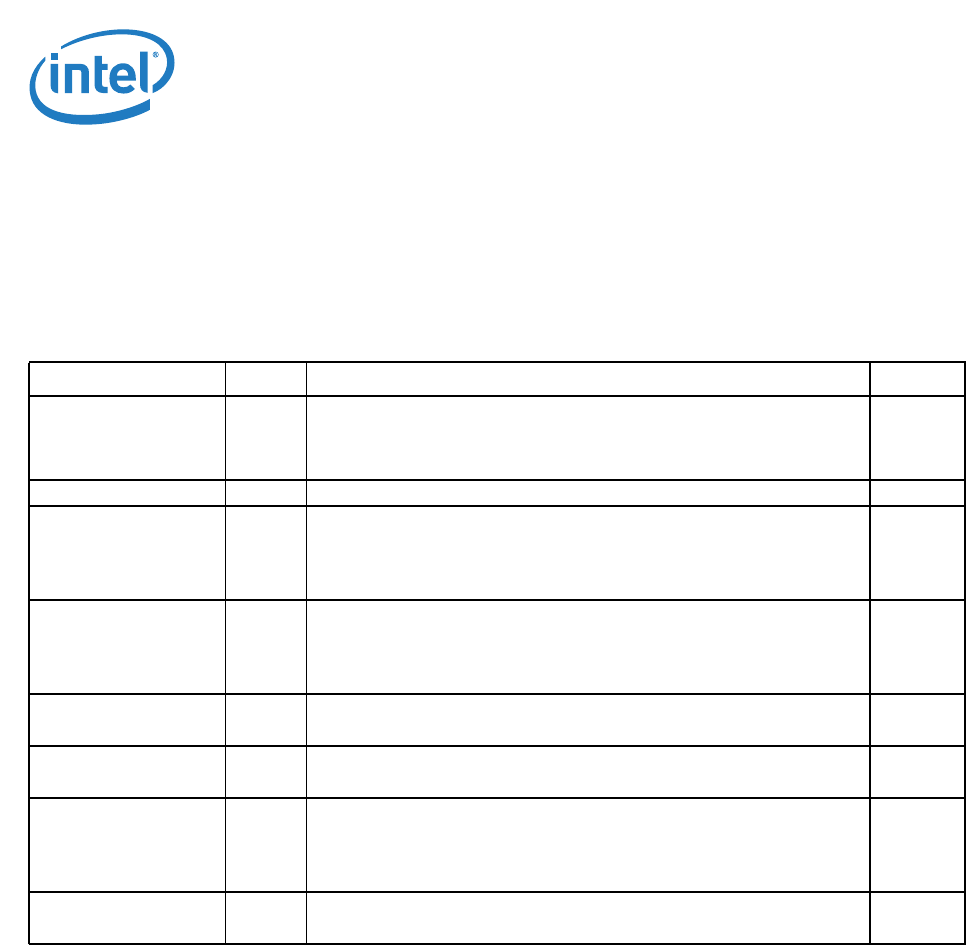

14.3.8.11 1000BASE-T/100BASE-T2 Status Register - GSTATUS

(10d; R)

1. The default of this bit is affected by the EEPROM bit configuration of the 82575.

If EEPPROM bit AN-1000DIS is asserted, then the default is set to 0b.

If EEPPROM bit ADV10LU (word 21h, bit 3) is asserted, then the default is set to 0b.

Field Bit(s) Description Mode

Idle Error Count 7:0 Idle Error counter Value.

This register counts the number of invalid idle codes when link is high and

the PHY is in either 1000BASE-T or 100BASE-T modes. If an overflow, these

bits are held at all 1b. They are cleared on read or a hard or soft reset.

RO, LH

Reserved 9:8 Reserved. Always set to 00b. RO

LP 1000T HD 10 1b = Link Partner is capable of 1000BASE-T half duplex.

0b = Link Partner is not capable of 1000BASE-T half duplex.

Values in bits 11:10 are not valid until the ANE Register Page Received bit

equals 1b.

RO

LP 1000T FD 11 1b = Link Partner is capable of 1000BASE-T full duplex.

0b = Link Partner is not capable of 1000BASE-T full duplex.

Values in bits 11:10 are not valid until the ANE Register Page Received bit

equals 1b.

RO

Remote Receiver Status 12 1b = Remote Receiver OK.

0 b = Remote Receiver Not OK.

RO

Local Receiver Status 13 1b = Local Receiver OK.

0b = Local Receiver Not OK.

RO

Master/Slave Resolution 14 1b = Local PHY configuration resolved to Master.

0b = Local PHY configuration resolved to Slave.

Values in bits 11:10 are not valid until the ANE Register Page Received bit

equals 1b.

RO

Master/Slave

Config Fault

15 1b = Master/Slave configuration fault detected.

0b = No Master/Slave configuration fault detected.

RO, LH