Intel

®

82575EB Gigabit Ethernet Controller — MSI-X Table Entry Lower Address - MSIXTADD

(00000h - 00090h; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

446 January 2011

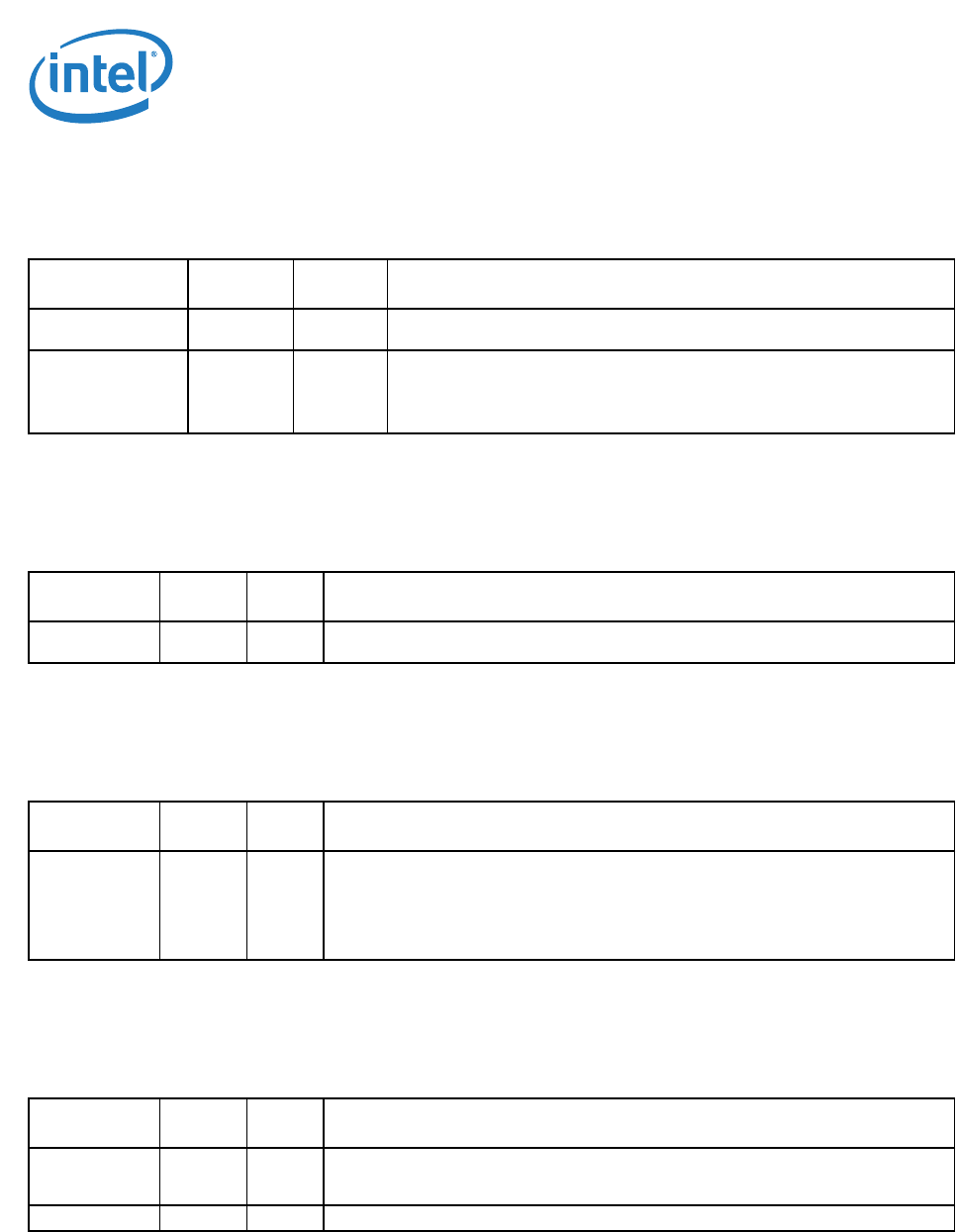

14.12.1 MSI-X Table Entry Lower Address - MSIXTADD

(00000h - 00090h; R/W)

14.12.2 MSI-X Table Entry Upper Address - MSIXTUADD

(BAR3: 0004h + n*10h [n=0..9]; RW)

14.12.3 MSI-X Table Entry Message - MSIXTMSG (BAR3:

0008h + n*10h [n=0..9]; RW)

14.12.4 MSI-X Table Entry Vector Control - MSIXVCTRL

(BAR3: 000Ch + n*10h [n=0..9]; RW)

Field Bit(s)

Initial

Value

Description

Message Address

LSB (RO)

1:0 0h For proper DWORD alignment, software must always write 0b’s to these two

bits. Otherwise, the result is undefined.

Message Address 31:2 0h System-Specific Message Lower Address

For MSI-X messages, the contents of this field from an MSI-X table entry

specifies the lower portion of the DWORD-aligned address for the memory

write transaction.

Field Bit(s)

Initial

Value

Description

Message

Address

31:0 0h System-Specific Message Upper Address

Field Bit(s)

Initial

Value

Description

Message Data 31:0 0h System-Specific Message Data

For MSI-X messages, the contents of this field from an MSI-X table entry specifies the

data written during the memory write transaction.

In contrast to message data used for MSI messages, the low-order message data bits

in MSI-X messages are not modified by the function.

Field Bit(s)

Initial

Value

Description

Mask 0 1b When this bit is set, the function is prohibited from sending a message using this MSI-

X table entry. However, any other MSI-X table entries programmed with the same

vector are still capable of sending an equivalent message unless they are also masked.

Reserved 31:1 0h Reserved