Intel

®

82575EB Gigabit Ethernet Controller — Device Control Register - CTRL (00000h; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

300 January 2011

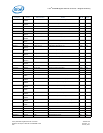

Field Bit(s)

Initial

Value

Description

FD 0 1b Full-Duplex

Controls the MAC duplex setting when explicitly set by software.

0b = half duplex.

1b = full duplex.

Reserved 1 0b This bit is reserved and should be set to 0b for future compatibility.

GIO Master

Disable

2 0b When set to 1b, the function of this bit blocks new master requests including

manageability requests. If no master requests are pending by this function, the GIO

Master Enable Status bit is set.

Reserved 3 1b

1

Reserved

Reserved 4 0b

1

Reserved

Factory use only. Should be written with 0b.

Reserved 5 0b

1

Reserved

Must be set to 0b.

SLU 6 0b

1

Set Link Up

When the MAC link mode is set for 10/100/1000Base-T mode (internal PHY), Set

Link Up must be set to 1b to permit the MAC to recognize the LINK signal from the

PHY, which indicates the PHY has gotten the link up, and to receive and transmit

data.

The Set Link Up is normally initialized to 0b. However, if the APM Enable bit (bit 10)

of Word 14/24 is set in the EEPROM then it is initialized to 1b.

ILOS 7 0b

1

Invert Loss-of-Signal (LOS/LINK) Signal

0b = Do not invert (active high input signal).

1b = Invert signal (active low input signal).

SPEED 9:8 10b Speed selection.

These bits determine the speed configuration and are written by software after

reading the PHY configuration through the MDIO interface.

These signals are ignored when Auto-Speed Detection is enabled.

00b = 10 Mb/s.

01b = 100 Mb/s.

10b = 1000 Mb/s.

11b = not used.

Reserved 10 0b Reserved

Write as 0b to ensure future compatibility.

FRCSPD 11 0b

1

Force Speed

This bit is set when software needs to manually configure the MAC speed settings

according to the SPEED bits. When using a PHY device, note that the PHY device

must resolve to the same speed configuration or software must manually set it to

the same speed as the MAC. The default is asserted. Software must clear this bit to

enable the PHY or ASD function to control the MAC speed setting. Note that this bit

is superseded by the CTRL_EXT.SPD_BYPS bit which has a similar function.

FRCDPLX 12 0b Force Duplex

When set to 1b, software can override the duplex indication from the PHY that is

indicated in the FDX to the MAC. Otherwise, in 10/100/1000Base-T link mode, the

duplex setting is sampled from the PHY FDX indication into the MAC on the asserting

edge of the PHY LINK signal. When asserted, the CTRL.FD bit sets duplex.

Reserved 15:13 000b Reserved

Reads as 000b.