Intel

®

82575EB Gigabit Ethernet Controller — Integrated 10/100/1000 Mb/s PHY

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

22 January 2011

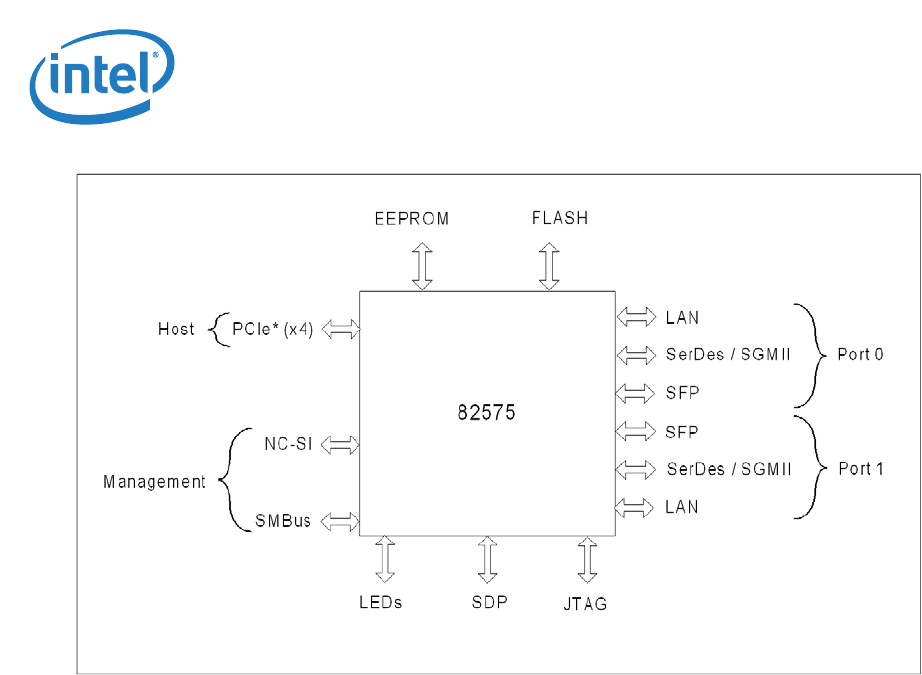

Figure 1. 82575 External Interfaces

2.1.1 Integrated 10/100/1000 Mb/s PHY

The 82575 contains integrated 10/100/1000 Mb/s-capable Copper PHY's. Each of these PHY's

communicate with its MAC controllers using a standard 10/100/1000Base-T interface internal to the

component to transfer transmit and receive data. A standard MDIO interface, accessible to software via

MAC control registers, is also used to configure and monitor each PHY operation.

2.1.2 System Interface

The 82575 provides 4 lanes of PCIe* bus interface working at 2.5 GHz each, this should provide

sufficient bandwidth to support sustained dual port of 1000 Mb/s transfer rates. 48 KB of on-chip

buffering mitigates instantaneous receive bandwidth demands and eliminates transmit under-runs by

buffering the entire outgoing packet prior to transmission.

2.1.3 EEPROM Interface

The 82575 provides a four-wire direct interface to a serial EEPROM device such as the 93C46 or

compatible for storing product configuration information. Several words of the data stored in the

EEPROM are automatically accessed by the 82575, after reset, to provide pre-boot configuration data to

the 82575 before it is accessible by the host software. The remainder of the stored information is

accessed by various software modules to report product configuration, serial number and other

parameters.

Note: An EEPROM is required for normal operation.