Intel

®

82575EB Gigabit Ethernet Controller — Transmit Descriptor Base Address Low - TDBAL

(03800h + 100*n [n=0..3]; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

366 January 2011

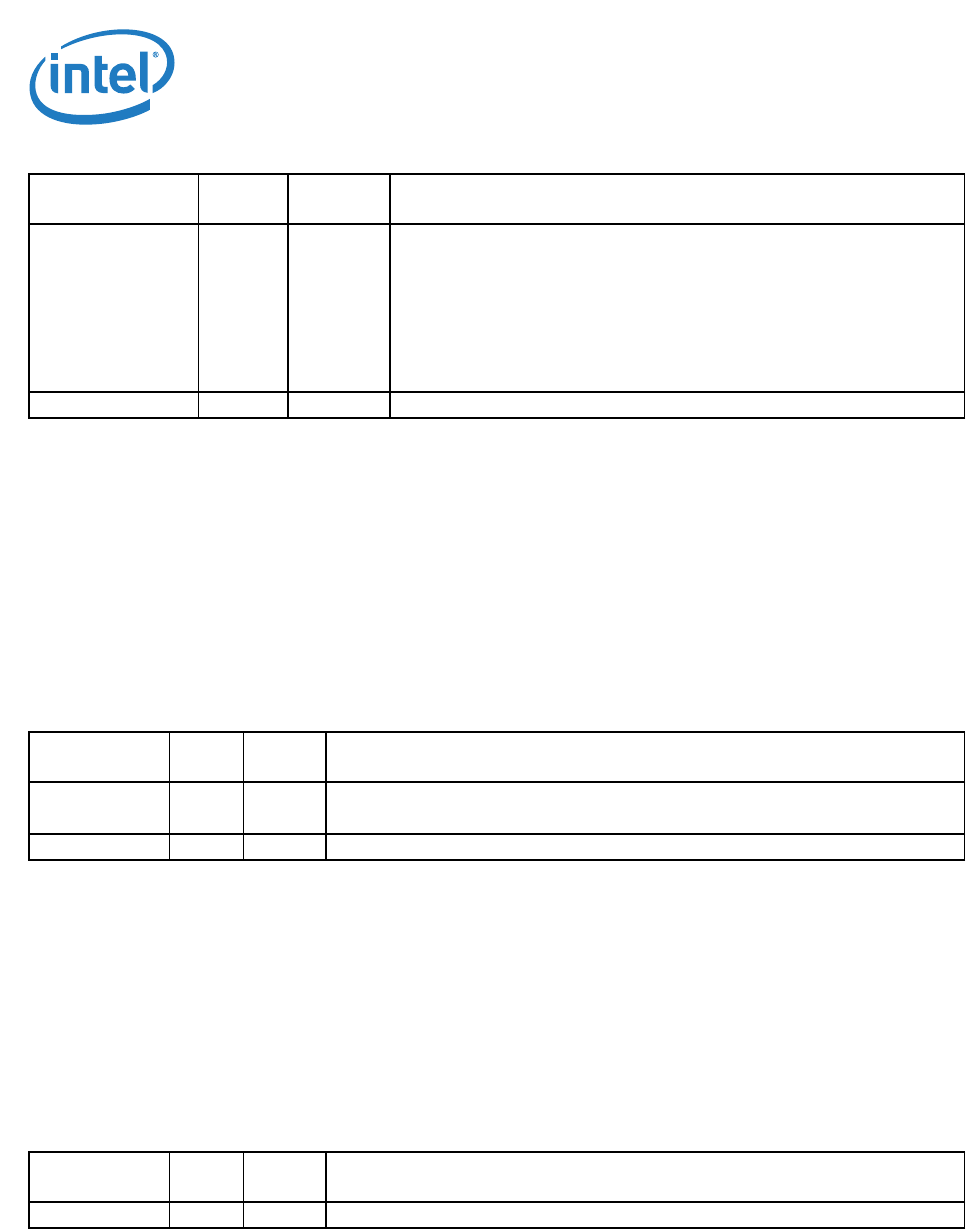

14.3.68 Transmit Descriptor Base Address Low - TDBAL

(03800h + 100*n [n=0..3]; R/W)

These registers contain the lower bits of the 64-bit descriptor base address. The lower 4 bits are

ignored. The Transmit Descriptor Base Address must point to a 128-byte aligned block of data.

• Queue0 - TDBAL0 (03800h)

• Queue1 - TDBAL1 (03900h)

• Queue2 - TDBAL2 (03A00h)

• Queue3 - TDBAL3 (03B00h)

14.3.69 Transmit Descriptor Base Address High - TDBAH

(03804h + 100*n [n=0..3]; R/W)

These registers contain the upper 32 bits of the 64-bit descriptor base address.

• Queue0 - TDBAH0 (03804h)

• Queue1 - TDBAH1 (03904h)

• Queue2 - TDBAH2 (03A04h)

• Queue3 - TDBAH3 (03B04h)

Field Bit(s)

Initial

Value

Description

IPID_15‘ 0 0b IP Identification 15-Bit

When set to 1b, the IP identification field increments and wraps around on 15-

bit base. For example, if IP ID is equal to 7FFFh then the next value is 0000h;

if IP ID is equal to FFFFh then the next value is 8000h.

When set to 0b, the IP Identification field increments and wraps around on 16-

bit base. In this case, the value following 7FFFh is 8000h and the value

following FFFFh is 0000h.

This feature enables software to manage two subgroups of connections.

Reserved 31:1 0h Reserved

Field Bit(s)

Initial

Value

Description

Reserved 6:0 00h Ignored on writes.

Returns 00h on reads.

TDBAL 31:7 X Transmit Descriptor Base Address Low

Field Bit(s)

Initial

Value

Description

TDBAH 31:0 X Transmit Descriptor Base Address [63:32]