Intel

®

82575EB Gigabit Ethernet Controller — Receive Descriptor Base Address High - RDBAH

(02804h + 100*n [n=0..3]; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

358 January 2011

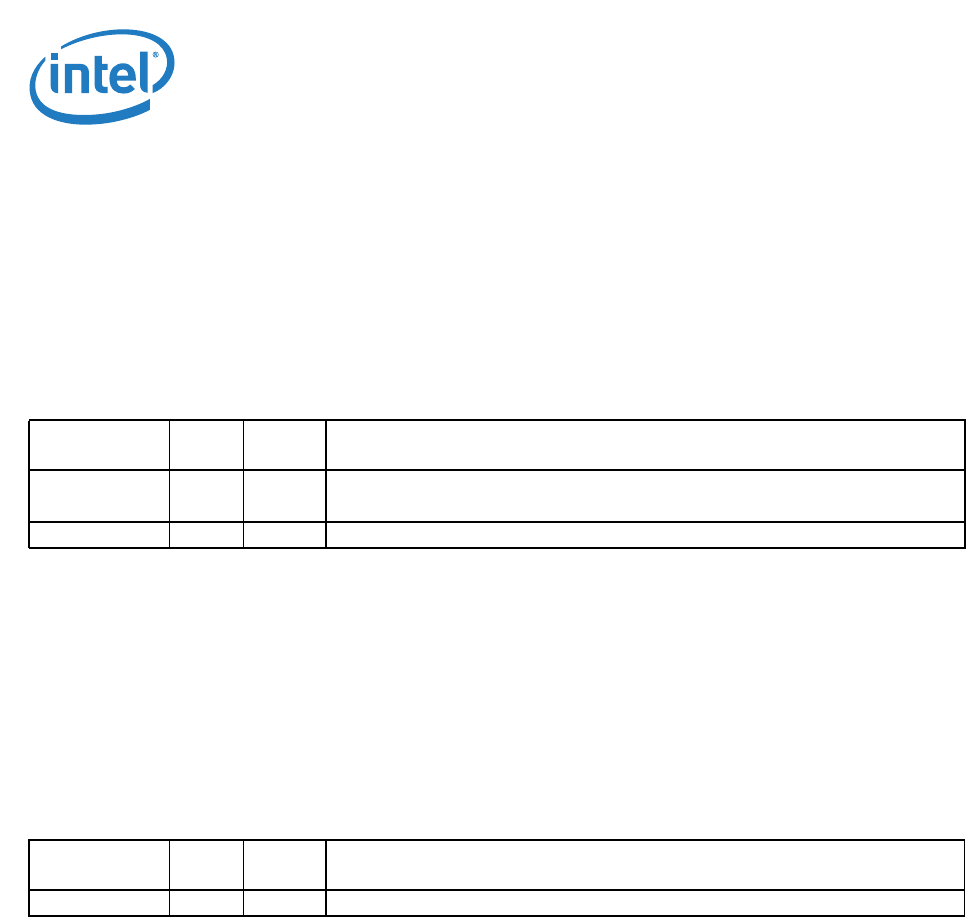

14.3.55.1 Receive Descriptor Base Address Low - RDBAL

(02800h + 100*n [n=0..3]; R/W)

This register contains the lower bits of the 64-bit descriptor base address. The lower four bits are

always ignored. The Receive Descriptor Base Address must point to a 128 byte-aligned block of data.

• Queue0 - RDBAL0 (02800h)

• Queue1 - RDBAL1 (02900h)

• Queue2 - RDBAL2 (02A00h)

• Queue3 - RDBAL3 (02B00h)

14.3.56 Receive Descriptor Base Address High - RDBAH

(02804h + 100*n [n=0..3]; R/W)

This register contains the upper 32 bits of the 64-bit descriptor base address

• Queue0 - RDBAH0 (02804h)

• Queue1 - RDBAH1 (02904h)

• Queue2 - RDBAH2 (02A04h)

• Queue3 - RDBAH3 (02B04h)

14.3.57 Receive Descriptor Length - RDLEN (02808h +

100*n [n=0..3]; R/W)

This register sets the number of bytes allocated for descriptors in the circular descriptor buffer. It must

be 128-byte aligned.

• Queue0 - RDLEN0 (02808h)

• Queue1 - RDLEN1 (02908h)

• Queue2 - RDLEN2 (02A08h)

• Queue3 - RDLEN3 (02B08h)

Field Bit(s)

Initial

Value

Description

Reserved 6:0 00h Ignored on writes.

Returns 00h on reads.

RDBAL 31:7 X Receive Descriptor Base Address Low

Field Bit(s)

Initial

Value

Description

RDBAH 31:0 X Receive Descriptor Base Address [63:32]