Tx Descriptor Completion Write-Back Address Low - TDWBAL (03838h + 100*n [n=0..3]; R/W)

— Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 369

14.3.74 Tx Descriptor Completion Write-Back Address

Low - TDWBAL (03838h + 100*n [n=0..3]; R/

W)

• Queue0 - TDWBAL0 (03838h)

• Queue1 - TDWBAL1 (03938h)

• Queue2 - TDWBAL2 (03A38h)

• Queue3 - TDWBAL3 (03B38h)

Reserved 24:22 00h Reserved

ENABLE 25 1/0b Transmit Queue Enable

When set, this bit enables the operation of a specific transmit queue:

Default value for Q0 = 1b.

Default value for Q3:1 = 0b.

Setting this bit initializes all the internal registers of a specific queue. Until then, the

state of the queue is kept and can be used for debug purposes.

When disabling a queue, this bit is cleared only after all activity at the queue stopped.

Note: This bit is valid only if the queue is actually enabled, thus if RCTL.RXEN is

cleared, this bit remain 0b.

SWFLSH 26 0b Transmit Software Flush

This bit enables software to trigger descriptor write-back flushing, independently of

other conditions.

This bit is self cleared by hardware.

Priority 27 0b Priority

Sets the arbitration priority for this queue.

0b = Low priority.

1b = High priority.

Reserved 31:28 0h Reserved

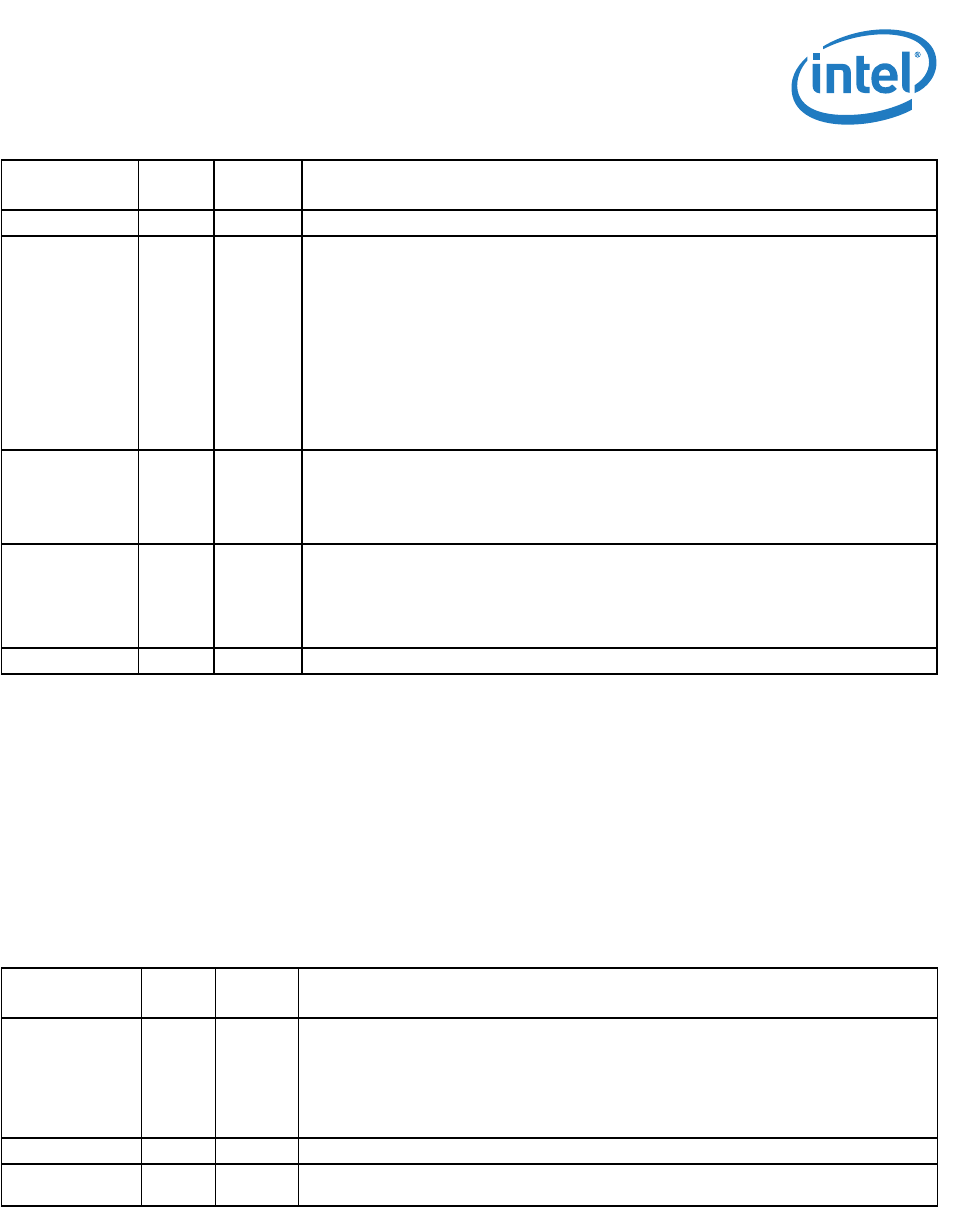

Field Bit(s)

Initial

Value

Description

Head_WB_En 0 0b Head Write-Back Enable

1b = Head write-back enabled.

0b = Head write-back is disabled.

When head_WB_en is set, SN_WB_en is ignored and no descriptor write-back is

executed.

Reserved 1 0b Reserved

HeadWB_Low 31:2 0h Lowest 32 bits of the head write-back memory location (DWORD aligned). Note that the

last two bits are always 00b.

Field Bit(s)

Initial

Value

Description