Multiple Receive Queues — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 119

These registers hold a value that is an offset from the base and indicates the in-progress descriptor.

There can be up to 8 KB descriptors in the circular buffer. Hardware maintains a shadow copy that

includes those descriptors completed but not yet stored in memory.

• Receive Descriptor Tail registers (RDT0, RDT1, RDT2, RDT3)

These registers hold a value that is an offset from the base and identifies the location beyond the

last descriptor hardware can process. This is the location where software writes the first new

descriptor.

If software statically allocates buffers, and uses memory read to check for completed descriptors, it

simply has to zero the status byte in the descriptor to make it ready for re-use by hardware. This is not

a hardware requirement, but is necessary for performing an in-memory scan.

All the registers controlling the descriptor rings behavior should be set before receive is enabled, apart

from the tail registers which are used during the regular flow of data.

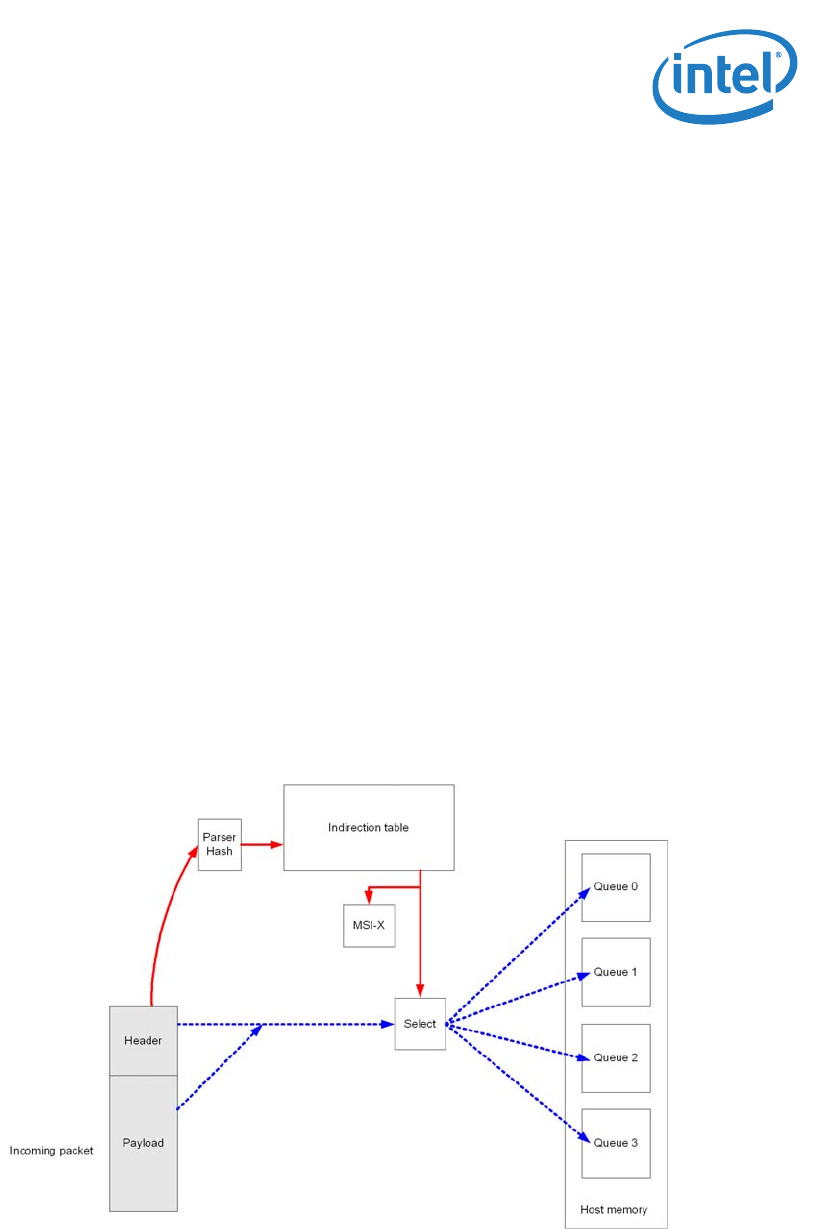

5.4 Multiple Receive Queues

The 82575 supports four receive descriptor Queues organized in ring structures. The ring functionality

is described in Section 5.3.8. The four receive queues are intended for use with the Receive Side

Scaling (RSS) algorithm. The following figure shows the implementation of multiple receive queues in

connection with RSS.

Note: For more information on manageability, refer to the 82575 TCO/System Manageability

Interface Application Note (AP-495).

Figure 4. Multiple Queues in Receive

First, the software application stores into the indirection table a set of values, enabling pre-determined

indirection of incoming packets to specific queues, each queue being dedicated to one processor. This

enables load balancing of multiple connections among the processors.