Intel

®

82575EB Gigabit Ethernet Controller — Register Conventions

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

288 January 2011

• Register pairs where two 32-bit registers make up a larger logical size.

• Accesses to Flash memory (through the Expansion ROM space, secondary BAR space, or the I/O

space) can be byte, word, or double word accesses.

Reserved bit positions. Some registers contain certain bits that are marked as “reserved.” These bits

should never be set to a value of 1b by software. Reads from registers containing reserved bits can

return indeterminate values in the reserved bit positions unless read values are explicitly stated. When

read, these reserved bits should be ignored by software.

Reserved and/or undefined addresses. Any register address not explicitly declared in this

specification should be considered to be reserved and should not be written. Writing to reserved or

undefined register addresses can cause indeterminate behavior. Reads from reserved or undefined

configuration register addresses can return indeterminate values unless read values are explicitly

stated for specific addresses.

Initial values. Most registers define the initial hardware values prior to being programmed. In some

cases, hardware initial values are undefined and are listed as such via the text “undefined,” “unknown,”

or “X.” Some such values might need setting through EEPROM configuration or software in order for

proper operation to occur; this need is dependent on the function of the bit. Other registers might cite

a hardware default that is overridden by a higher precedence operation. Operations that might

supersede hardware defaults can include a valid EEPORM load, completion of a hardware operation

(such as hardware Auto-Negotiation), or writing of a different register whose value is then reflected in

another bit.

For registers that should be accessed as 32-bit double words, partial writes (less than a 32-bit double

word) is ignored. Partial reads return all 32 bits of data regardless of the byte enables.

Note: Partial reads to read-on-clear registers (like ICR) can have unexpected results since all 32

bits are actually read regardless of the byte enables. Partial reads should not be done.

All statistics registers are implemented as 32-bit registers. Though some logical statistics

registers represent counters in excess of 32-bits in width, registers must be accessed using

32-bit operations. For example, independent access to each 32-bit field.

Refer to the special notes for VLAN Filter Table, Multicast Table Arrays and Packet Buffer Memory

appears in the specific register definitions.

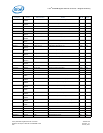

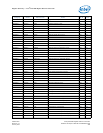

The 82575 register fields are assigned one of the attributes listed in Table 87.