Device Control Register - CTRL (00000h; R/W) — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 299

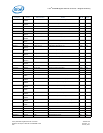

14.3.1 Device Control Register - CTRL (00000h; R/W)

This register, as well as the Extended Device Control register (CTRL_EXT), controls the major

operational modes for the 82575. While software writes to this register to control the 82575 settings,

several bits (such as FD and SPEED) can be overridden depending on other bit settings and the

resultant link configuration determined by the PHY's Auto-Negotiation resolution.

Note: In half-duplex mode, the 82575 transmits carrier extended packets and can receive both

carrier extended packets and packets transmitted with bursting.

When using an internal PHY or SGMII, the FD (duplex) and SPEED configuration of the 82575 is

normally determined from the link configuration process. Software can specifically override/set these

82575 MAC settings via these bits in a forced-link scenario; if so, the values used to configure the

82575 MAC must be consistent with the PHY settings.

When operating in SerDes mode, the SPEED field value is ignored. In SerDes mode with Auto-

Negotiation enabled, the FD bit is set to the negotiated duplex value.

If hardware AN is enabled, the transmitter sends configuration words until AN completes.

When the 82575 MAC is operating in a 10/100/1000BASE-T (internal PHY) mode, manual link

configuration is controlled through the PHY's 10/100BASE-T management interface.

A signal called LOS (loss-of-signal) indicates when no laser light is being received when the 82575 is

used in a 1000BASE-SX or -LX implementation. This prevents false carrier cases occurring when

transmission out a non-existent fiber couples into the input. Note that there is no standard polarity for

this signal coming from different manufacturers. The ILOS bit provides for inversion of the signal from

different external SerDes vendors and should be set when external SerDes provides a negative-true

loss-of-signal. This bit also inverts the LINK input that provides link status indication from the PHY (in

10/100/1000BASE-T mode) and therefore should be set to 0b for proper internal PHY operation.

The ADVD3WUC bit (Advertise D3Cold Wakeup Capability Enable control) enables the AUX_PWR pin to

determine whether D3Cold support is advertised. If full 1Gb/s operation in D3 state is desired but the

system’s power requirements in this mode would exceed the D3Cold Wakeup-Enabled specification limit

(375 mA at 3.3V), this bit can be used to prevent the capability from being advertised to the system.

When using the internal PHY, by default the PHY re-negotiates the lowest functional link speed in D3

and D0u states. The LPLU bit enables this capability to be disabled, if full 1Gb/s speed is desired in

these states.

Note: The 82575’s internal PHY automatically detects an unplugged LAN cable and reduces

operational power to the minimal amount required to maintain system operation. 82575

operations is not affected except for the inability to transmit/receive due to the lost link.

Device Reset (RST) can be used to globally reset the entire 82575. This register is provided as a

software mechanism to recover from an indeterminate or suspected hung hardware state. Most

registers (receive, transmit, interrupt, statistics, etc.), and state machines are set to their power-on

reset values, approximating the state following a power-on or PCI reset. However, PCIe* configuration

registers are not reset, thereby leaving the 82575 mapped into system memory space and accessible

by a software device driver. One internal configuration register, Packet Buffer Allocation (PBA), also

retains its value through a global reset.

Note: To ensure that global device reset has fully completed and that the 82575 responds to

subsequent accesses, an approximate one microsecond wait is required, after setting,

before attempting to check to see if the bit has cleared or to access (read or write) any

other 82575 register.