Extended Interrupt Auto Clear - EIAC (0152Ch; R/W) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 347

Software blocks interrupts by clearing the corresponding mask bit. This is accomplished by writing a 1b

to the corresponding bit location (as defined in the ICR register) of that interrupt in this register. Bits

written with 0b are unchanged (for example, their mask status does not change).

14.3.43 Extended Interrupt Auto Clear - EIAC (0152Ch;

R/W)

This register is mapped like the EICS, EIMS, and EIMC registers, with each bit mapped to the

corresponding bit in the EICR. EICR bits that have auto clear set are cleared when internally sent even

if the MSI-X message that they trigger is sent on the PCIe* bus is not set (masked). Note that the MSI-

X message can be delayed by EITR moderation from the time the EICR bit is activated. Bits without

auto clear set also need to be cleared with write-to-clear.

Note: Read-to-clear is not compatible with auto clear, so if any bits are set to auto clear, the EICR

register should not be read.

14.3.44 Extended Interrupt Auto Mask Enable - EIAM

(01530h; R/W)

Each bit in this register enables clearing of the corresponding bit in EIMS following read- or write-to-

clear to EICR or setting of the corresponding bit in EIMS following a write-to-set to EICS.

In MSI-X mode, this register controls which of the bits in EIMC to clear upon interrupt generation.

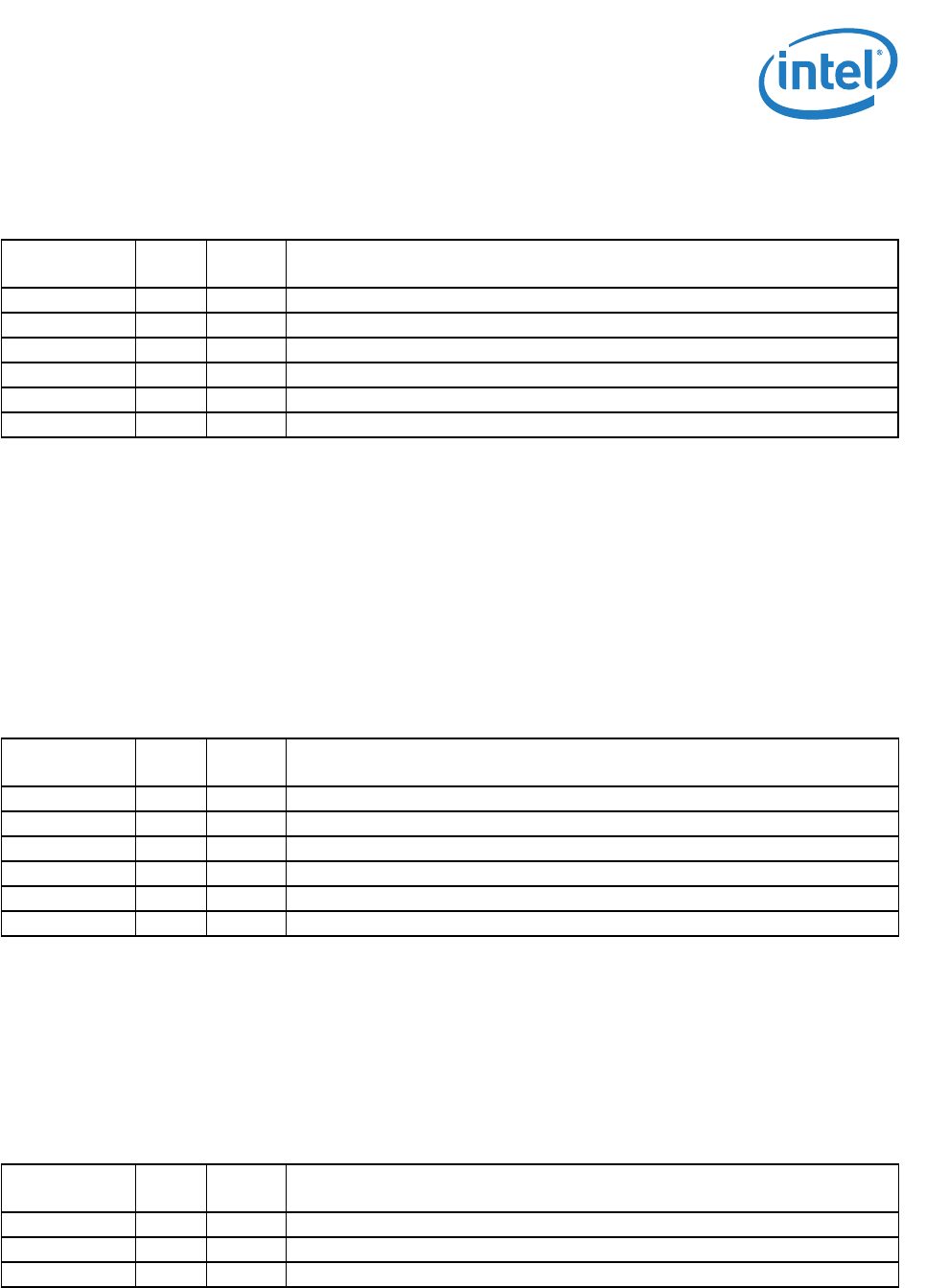

Field Bit(s)

Initial

Value

Description

RxQ 3:0 0000b Mask bit for the corresponding EICR RxQ interrupt condition.

Reserved 7:4 0000b Reserved

TxQ 11:8 0000b Mask bit for the corresponding EICR TxQ interrupt condition.

Reserved 29:12 0h Reserved

TCP Timer 30 0b Mask bit for the corresponding EICR TCP timer interrupt condition.

Other Cause 31 1b Mask bit for the corresponding EICR other cause interrupt condition.

Field Bit(s)

Initial

Value

Description

RxQ 3:0 0000b Auto clear bit for the corresponding EICR RxQ interrupt condition.

Reserved 7:4 0000b Reserved

TxQ 11:8 0000b Auto clear bit for the corresponding EICR TxQ interrupt condition.

Reserved 29:12 0h Reserved

TCP Timer 30 0b Auto clear bit for the corresponding EICR TCP timer interrupt condition.

Other Cause 31 1b Auto clear bit for the corresponding EICR other cause interrupt condition.

Field Bit(s)

Initial

Value

Description

RxQ 3:0 0000b Auto mask bit for the corresponding EICR RxQ interrupt condition.

Reserved 7:4 0000b Reserved

TxQ 11:8 0000b Auto mask bit for the corresponding EICR TxQ interrupt condition.