Intel

®

82575EB Gigabit Ethernet Controller — Tx Descriptor Completion Write-Back Address High

- TDWBAH (0383Ch + 100*n [n=0..3]; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

370 January 2011

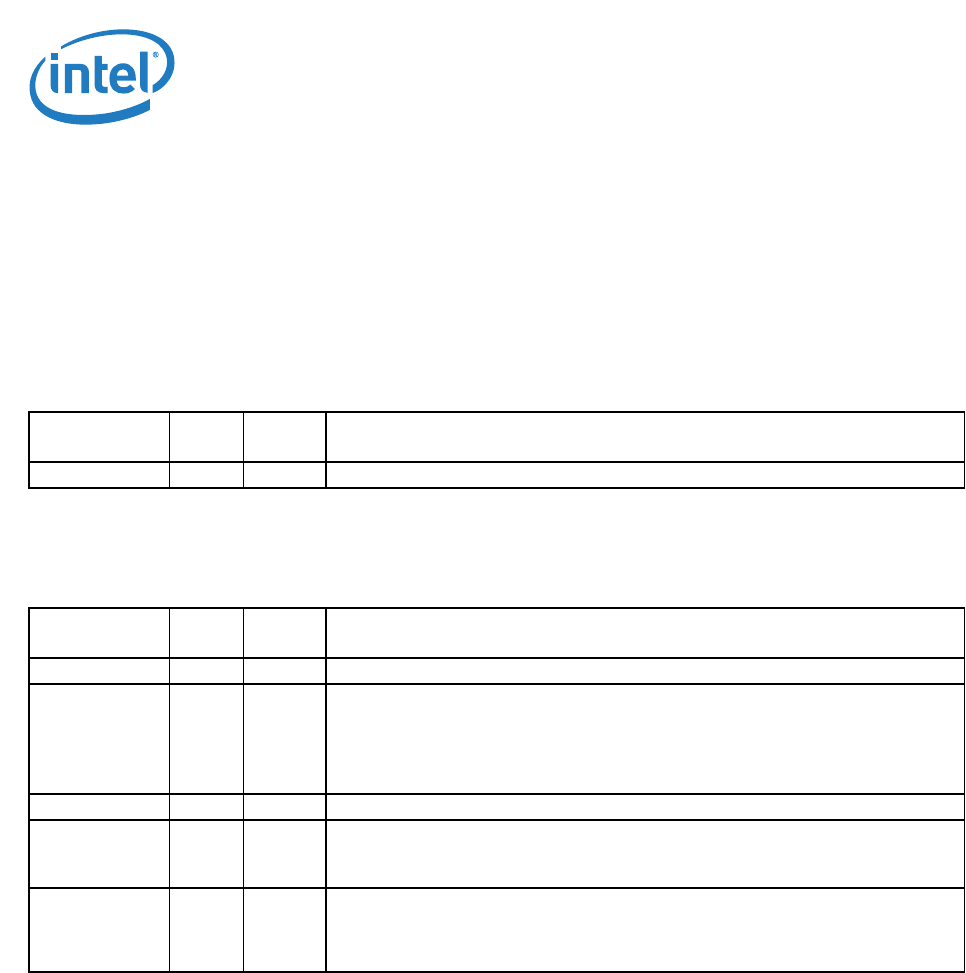

14.3.75 Tx Descriptor Completion Write-Back Address

High - TDWBAH (0383Ch + 100*n [n=0..3]; R/

W)

• Queue0 - TDWBAH0 (0383Ch)

• Queue1 - TDWBAH1 (0393Ch)

• Queue2 - TDWBAH2 (03A3Ch)

• Queue3 - TDWBAH3 (03B3Ch)

14.3.76 PCS Configuration 0 - PCS_CFG (04200h; R/W)

Field Bit(s)

Initial

Value

Description

HeadWB_High 31:0 0h Highest 32 bits of the head write-back memory location (for 64-bit addressing).

Field Bit(s)

Initial

Value

Description

Reserved 2:0 000b Reserved

PCS Enable 3 1b PCS Enable

Enables the PCS logic of the MAC. Should be set in both SGMII and SerDes mode for

normal operation.

Clearing this bit disables RX/TX of both data and control codes. Use this to force link

down at the far end.

Reserved 29:4 0h Reserved

PCS Isolate 30 0b PCS Isolate

Setting this bit isolates the PCS logic from the MAC's data path. PCS control codes are

still sent and received.

SRESET 31 0b Soft Reset

Setting this bit puts all modules within the MAC in reset except the Host Interface. The

Host Interface is reset via HRST. This bit is NOT self clearing; GMAC is in a reset state

until this bit is set.