Intel

®

82575EB Gigabit Ethernet Controller — Packet Buffer ECC Status - PBECCSTS (0245Ch; R/

W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

440 January 2011

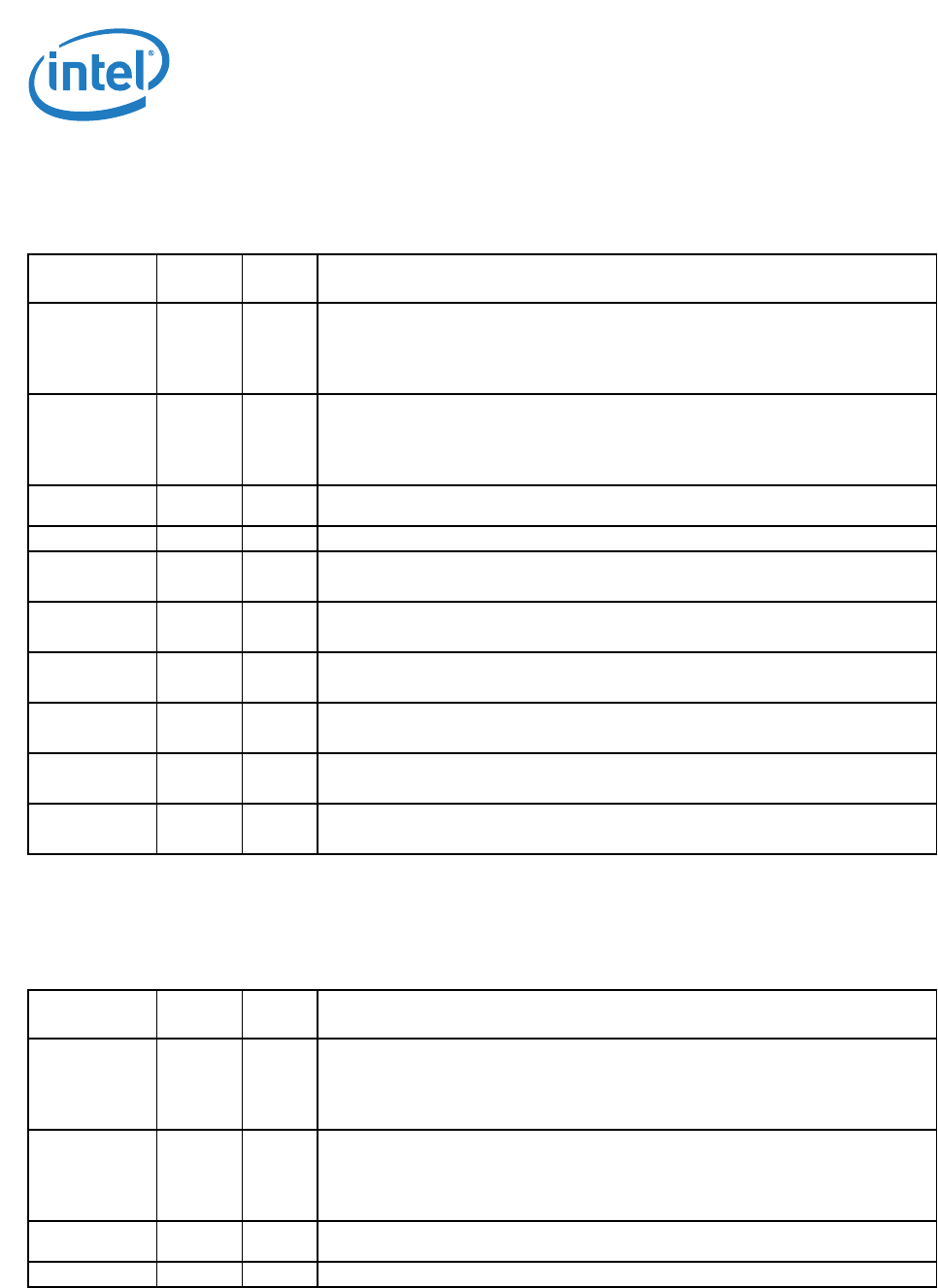

14.10.20 Packet Buffer ECC Status - PBECCSTS (0245Ch;

R/W)

14.10.21 Rx Descriptor Handler ECC Status - RDHESTS

(02468h; R/W)

Field Bit(s)

Initial

Value

Description

Corr_err_cnt 7:0 0h Correctable Error Count

This counter is increment every time a correctable error is detected; the counter stops

after reaching FFh.

These bits are cleared by reads.

Uncorr_err_cnt 15:8 0h Uncorrectable Error Count

This counter is increment every time an uncorrectable error is detected; the counter

stops after reaching FFh.

These bits are cleared by reads.

ECC Enable

(RW)

16 1b ECC Enable for Packet Buffer

Reserved 25:17 0b Reserved

Pb_cor_err_sta 26 0b Status of PB Correctable Error

This bit is cleared by a read.

Pb_uncor_err_

sta

27 0b Status of PB Uncorrectable Error

This bit is cleared by a read.

rx_desch_cor_

err_sts

28 0b Status of Rx Descriptor Handler Correctable Error

This bit is cleared by a read.

rx_desch_

uncor_err_sts

29 0b Status of Rx Descriptor Handler Uncorrectable Error

This bit is cleared by a read.

tx_desch_cor_

err_sts

30 0b Status of Tx Descriptor Handler Correctable Error

This bit is cleared by a read.

tx_desch_

uncor_err_sts

31 0b Status of Tx Descriptor Handler Uncorrectable Error

This bit is cleared by a read.

Field Bit(s)

Initial

Value

Description

Corr_err_cnt 7:0 0h Correctable Error Count

This counter is increment every time a correctable error is detected in the Rx descriptor

handler memory; the counter stops after reaching FFh.

These bits are cleared by reads.

Uncorr_err_cnt 15:8 0h Uncorrectable Error Count

This counter is increment every time a correctable error is detected in the Rx descriptor

handler memory; the counter stops after reaching FFh.

These bits are cleared by reads.

RDHECC

Enable

16 1b Rx Descriptor Handler ECC Enable

Reserved 31:17 0b Reserved