Intel

®

82575EB Gigabit Ethernet Controller — PHY Registers

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

324 January 2011

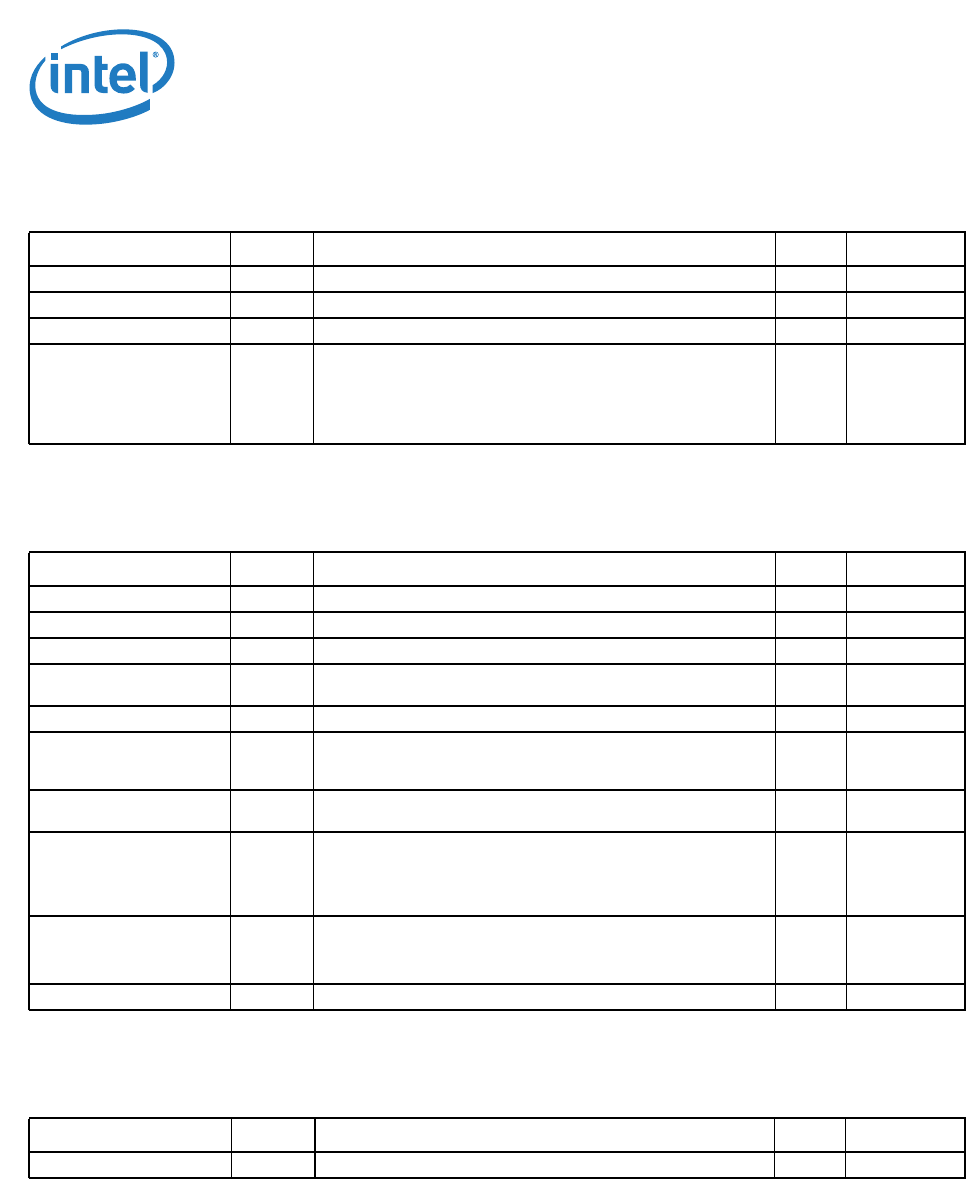

14.3.8.18 Channel Quality Register - CHAN (21d; RO)

14.3.8.19 PHY Power Management - (25d; R/W)

14.3.8.20 Special Gigabit Disable Register - (26d; R/W)

Field Bit(s) Description Mode Default

MSE_A 3:0 The converged mean square error for Channel A. RO 0b

MSE_B 7:4 The converged mean square error for Channel B. RO 0b

MSE_C 11:8 The converged mean square error for Channel C. RO 0b

MSE D 15:12 The converged mean square error for Channel D. This field is

only meaningful in gigabit, or in 100BASE-TX if this is the

receive pair.

Use of this field is complex and needs interpretation based on

the chosen threshold value.

RO 0b

Field Bit(s) Description Mode Default

Reserved 15:9 Always read as 0b. Write to 0b for normal operation. R/W 0b

rst_compl 8 Indicates PHY internal reset cleared. LH 0b

Reserved 7 Reserved. R/W 0b

Disable 1000 6 When set, disables 1000 Mb/s in all power modes. Note that

this bit can be loaded from EEPROM.

R/W 0b

Reserved 5 Always read as 0b. Write to 0b for normal operation. R/W 0b

Link Energy Detect 4 This bit is set when the PHY detects energy on the link. Note

that this bit is valid only if AN enabled (PHY register 00b, bit

12) and SPD_EN is enabled (PHY register 25d, bit 0).

R/W 0b

Disable 1000 nD0a 3 Disables 1000 Mb/s operation in non-D0a states. Note that

this bit can be loaded from EEPROM.

R/W 0b

LPLU 2 Low Power on Link Up

When set, enables the decrease in link speed while in non-

D0a states when the power policy and power management

state specify it. Note that bit can be loaded from EEPROM.

R/W 1b

D0LPLU 1 D0 Low Power Link Up

When set, configures the PHY to negotiate for a low speed link

while in D0a state.

R/W 0b

Reserved 0 Reserved R/W 0b

Field Bit(s) Description Mode Default

Reserved 15:0 Always read as 0b. Write to 0b for normal operation. R/W 0h