Mandatory PCI Configuration Registers — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 191

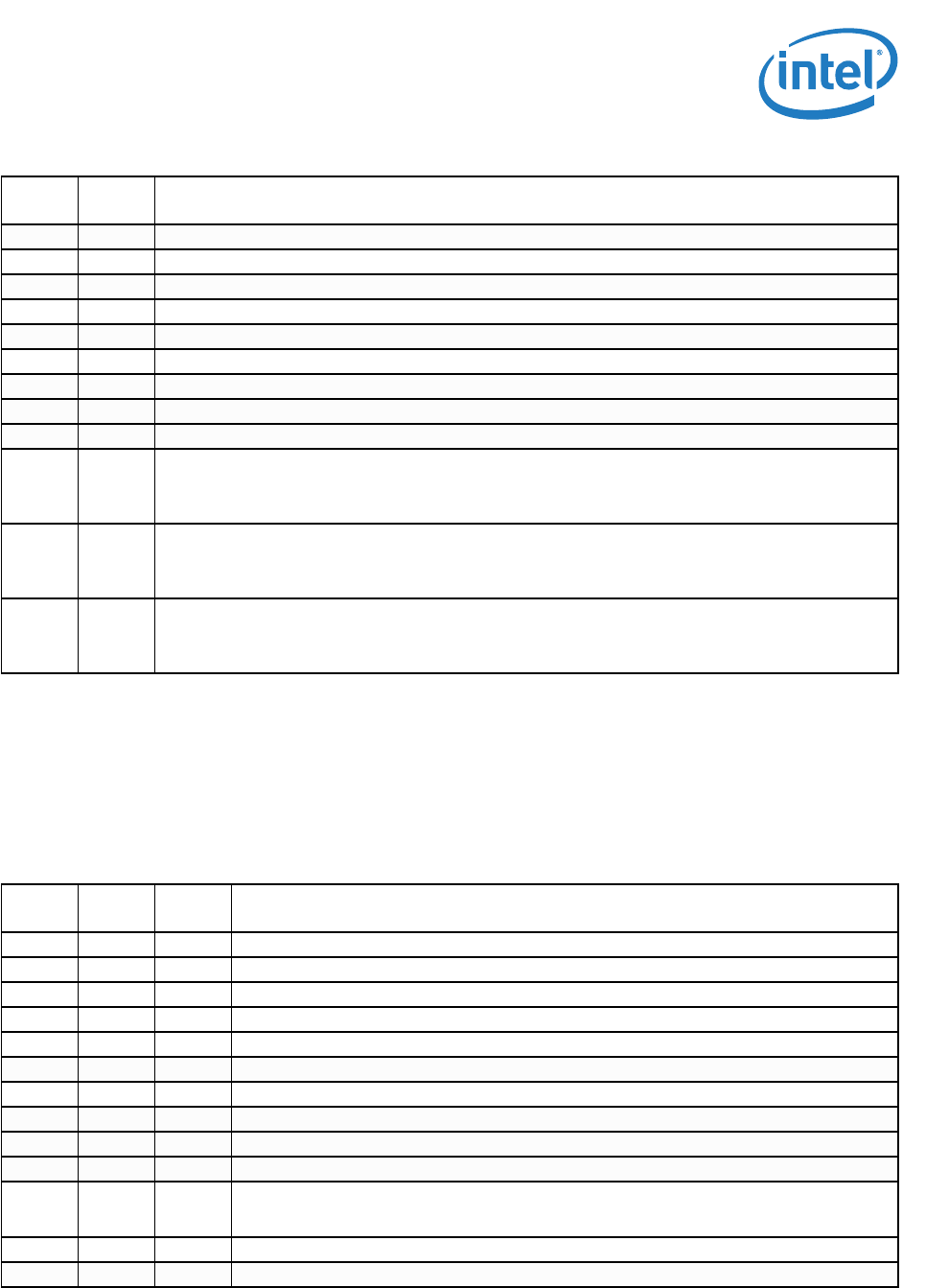

Status Register

Shaded bits are not used by this implementation and are hardwired to 0b. Each function has its own

status register. Unless explicitly specified, functionality is the same in all functions.

Bit(s)

Initial

Value

Description

15:11 0b Reserved.

10 0b Interrupt Disable.

1

1. The Interrupt Disable register bit is a read-write bit that controls the ability of a PCIe* device to

generate a legacy interrupt message. When set, devices are prevented from generating legacy

interrupt messages.

9 0b Fast Back-to-Back Enable. Hardwired to 0b.

8 0b SERR# Enable.

7 0b Wait Cycle Enable. Hardwired to 0b.

6 0b Parity Error Response.

5 0b Palette Snoop Enable. Hardwired to 0b.

4 0b MWI Enable. Hardwired to 0b.

3 0b Special Cycle Monitoring. Hardwired to 0b.

2 0b Enable Mastering:

LAN functions - R/W field.

Dummy function - RO as zero field.

1 0b Memory Access Enable:

LAN functions - R/W field.

Dummy function - RO as zero field.

0 0b I/O Access Enable:

LAN functions - R/W field.

Dummy function - RO as zero field.

Bit(s)

Initial

Value

RD/WR Description

15 0b R/W1C Detected Parity Error.

14 0b R/W1C Signaled System Error.

13 0b R/W1C Received Master Abort.

12 0b R/W1C Received Target Abort.

11 0b R/W1C Signaled Target Abort.

10:9 00b DEVSEL Timing. Hardwired to 0b.

8 0b R/W1C Data parity reported.

7 0b Fast Back-to-Back Capable. Hardwired to 0b.

6 0b Reserved.

5 0b 66 MHz Capable. Hardwired to 0b.

4 1b RO New Capabilities. This indicates that a device implements Extended Capabilities. The 82575

sets this bit and implements a capabilities list indicating it support for PCI Power Management,

message signaled interrupts, and the PCIe* extensions.

3 0b RO Interrupt Status.

1

2:0 0b Reserved.