Intel

®

82575EB Gigabit Ethernet Controller — Legacy Receive Descriptor Format

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

106 January 2011

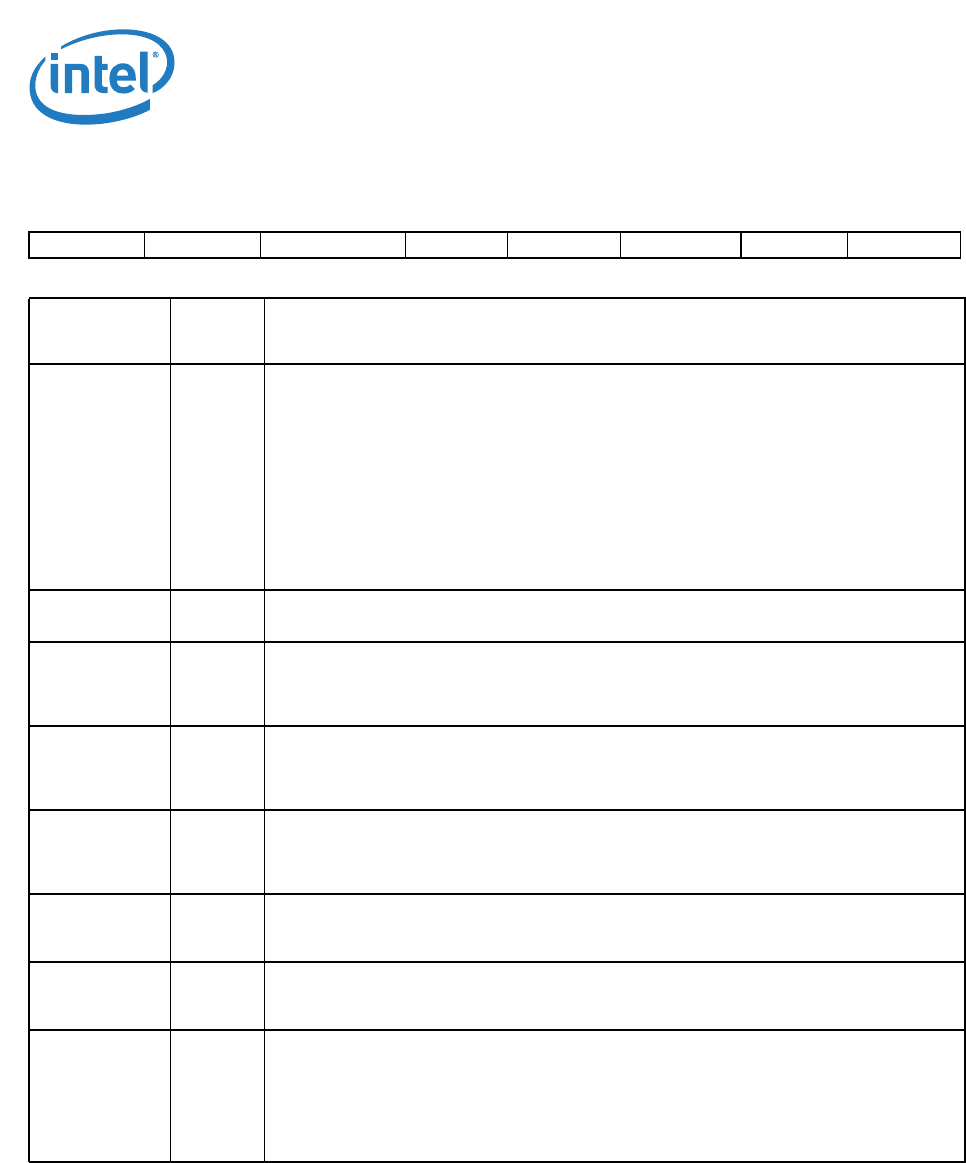

Table 28. Receive Status (RDESC.STATUS) Layout

Note: See Table 34 for a description of supported packet types for receive checksum offloading.

Unsupported packet types either have the IXSM bit set, or they don’t have the IPCS or

TCPCS bits set. IPv6 packets do not have the IPCS bit set, but might have the TCPCS bit set

if the 82575 recognized the TCP or UDP packet.

7 6 5 4 3 2 1 0

PIF IPCS TCPCS UDPCS VP IXSM EOP DD

Receive

Descriptor

Status Bits

Bit(s) Description

PIF 7 Passed In-Exact Filter.

Hardware supplies the PIF field to expedite software processing of packets. Software must

examine any packet with PIF set to determine whether to accept the packet. If PIF is clear, then

the packet is known to be for this station so software need not look at the packet contents. In

general, packets passing only the Multicast Vector (MTA) but not any of the MAC address exact

filters (RAH, RAL) has PIF set. In addition, the following condition causes PIF to be cleared:

The DA of the packet is a multicast address and promiscuous multicast is set (RCTL.MPE = 1b).

The DA of the packet is a broadcast address and accept broadcast mode is set (RCTL.BAM =

1b).

A MAC control frame forwarded to the host (RCTL.PMCF = 0b) that does not match any of the

exact filters, has the PIF bit set.

IPCS 6 IPv4 Checksum Calculated on Packet

If active, hardware provides IPv4 checksum offload.

TCPCS 5 TCP Checksum Calculated on Packet.

Hardware provides an IPv4 checksum offload if IPCS is active and TCP checksum is offload. A

pass/fail indication is provided in the Error field - IPE and TCPE. See Table 31 for supported

packet types.

UDPCS 4 UDP Checksum Calculated on Packet.

Hardware provides an IPv4 checksum offload if IPCS is active and UDP checksum is offload. A

pass/Fail indication is provided in the Error field - IPE and TCPE. See Table 31 for supported

packet types.

VP 3 Packet is 802.1q (matched VET).

The VP field indicates whether the incoming packet's type matches VET and VLAN field is strip

(For example, if the packet is a VLAN (802.1q) type). This bit is set if the packet type matches

VET and CTRL.VME is set.

IXSM 2 Ignore Checksum Indication.

When set to 1b, hardware does not provide checksum offload. Software device driver should

ignore the IPCS, TCPCS, and UDPCS bits.

EOP 1 End of Packet.

Packets that exceed the receive buffer size span multiple receive buffers. EOP indicates whether

this is the last buffer for an incoming packet.

DD 0 Descriptor Done.

indicates whether hardware is done with the descriptor. When set along with EOP, the received

packet is complete in main memory. Software can determine buffer usage by setting the status

byte to 0b before making the descriptor available to hardware and checking it for non-zero

content at a later time. For multi-descriptor packets, packet status is provided in the final

descriptor of the packet (EOP set). If EOP is not set for a descriptor, only the Address, Length,

and DD bits are valid.