PCI Power Management Registers — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 199

In contrast to the MSI capability structure, which directly contains all of the control/status information

for the function's vectors, the MSI-X capability structure instead points to an MSI-X Table structure and

a MSI-X Pending Bit Array (PBA) structure, each residing in Memory Space.

Each structure is mapped by a Base Address register (BAR) belonging to the function, located beginning

at 10h in Configuration Space. A BAR Indicator register (BIR) indicates which BAR, and a QWORD-

aligned Offset indicates where the structure begins relative to the base address associated with the

BAR. The BAR is permitted to be either 32-bit or 64-bit, but must map Memory Space. A function is

permitted to map both structures with the same BAR, or to map each structure with a different BAR.

The MSI-X Table structure typically contains multiple entries, each consisting of several fields: Message

Address, Message Upper Address, Message Data, and Vector Control. Each entry is capable of

specifying a unique vector.

The Pending Bit Array (PBA) structure contains the function's Pending Bits, one per Table entry,

organized as a packed array of bits within QWORDs.

The last QWORD is not necessarily be fully populated.

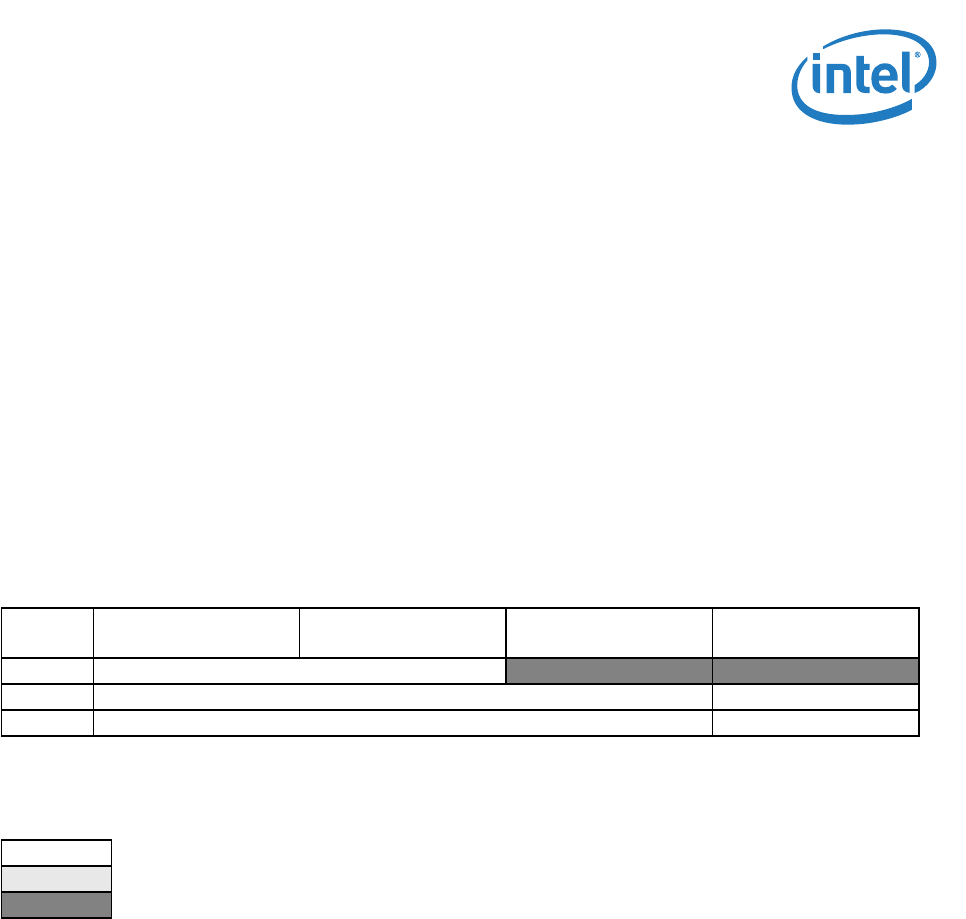

Note: The following color notation is used for reference:

Capability ID: 1 Byte, Offset 60h, (RO)

This field equals 11h indicating the linked list item as being the MSI-X registers.

Next Pointer: 1 Byte, Offset 61h, (RO)

This field provides an offset to the next capability item in the capability list. Its value of A0h points to

the PCIe* capability structure.

Message Control: 2 Byte, Offset 62h, (R/W)

The register fields are described in the table that follows. There is a dedicated register per PCI function

to enable separately their MSI.

Table 68. MSI-X Capability Structure

Byte

Offset

Byte 3 Byte 2 Byte 1 Byte 0

60h Message Control (0009h)

Next Pointer (0Ah) Capability ID (11h)

64h

1

1. Hardwired to 3h.

Table Offset Table BIR

68h

2

2. Hardwired to 2003h.

PBA Offset PBA BIR

Fields identical to all functions.

Read only fields.

Hard coded fields and strapping options.