Intel

®

82575EB Gigabit Ethernet Controller — DCA Control - DCA_CTRL (05B74h; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

416 January 2011

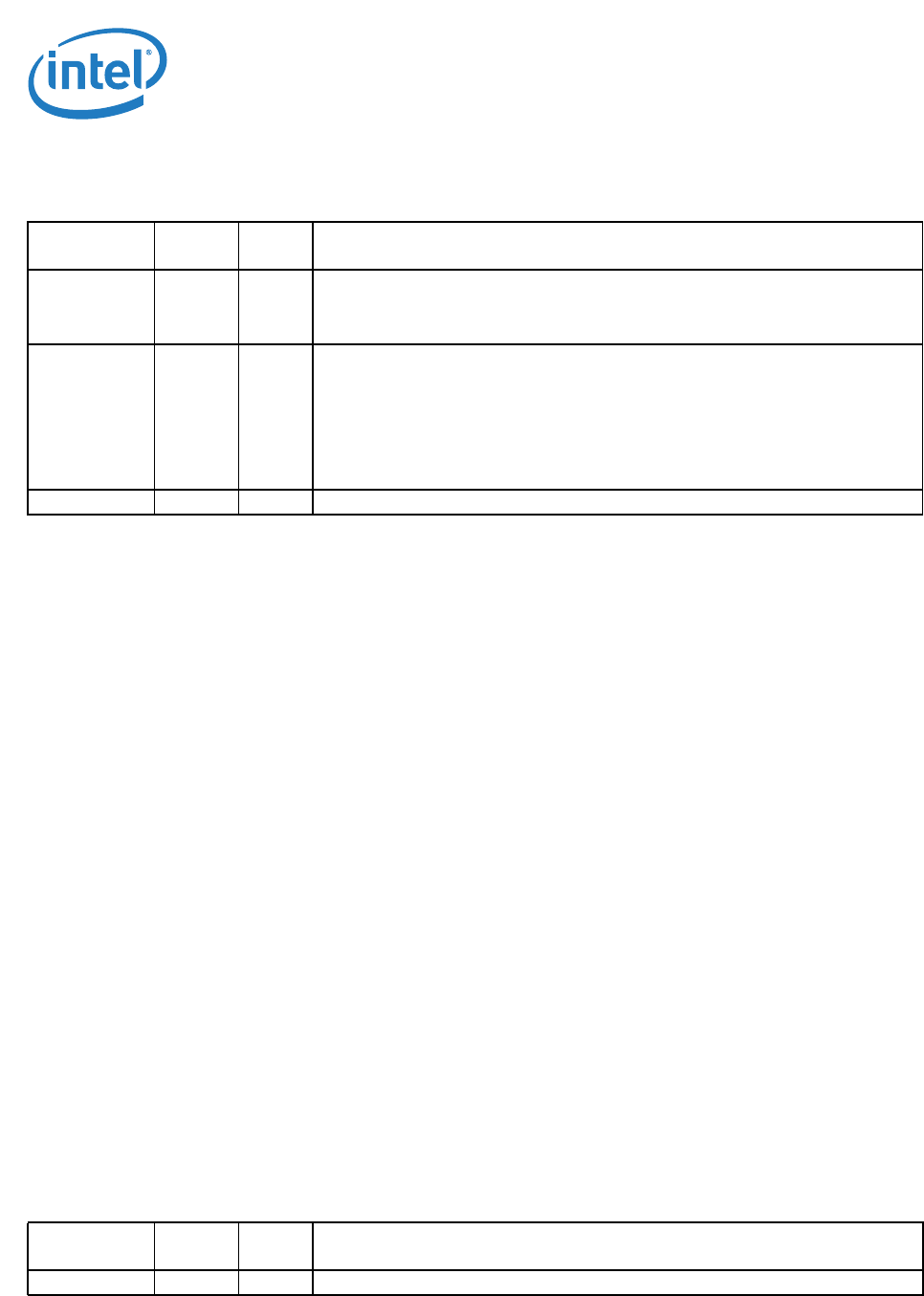

14.8.25 DCA Control - DCA_CTRL (05B74h; R/W)

Note: The DCA tag disabled value in data movement engine 2 mode in the 82575 A0 is 11111b.

14.9 Statistics Registers

All Statistics registers reset when read. In addition, they stick at FFFF_FFFFh when the maximum value

is reached.

For the receive statistics it should be noted that a packet is indicated as received if it passes the

82575's filters and is placed into the packet buffer memory. A packet does not have to be transferred to

host memory in order to be counted as received.

Due to divergent paths between interrupt-generation and logging of relevant statistics counts, it might

be possible to generate an interrupt to the system for a noteworthy event prior to the associated

statistics count actually being incremented. This is extremely unlikely due to expected delays

associated with the system interrupt-collection and ISR delay, but might be observed as an interrupt for

which statistics values do not quite make sense. Hardware guarantees that any event noteworthy of

inclusion in a statistics count is reflected in the appropriate count within 1 s; a small time-delay prior

to a read of statistics might be necessary to avoid the potential for receiving an interrupt and observing

an inconsistent statistics count as part of the ISR.

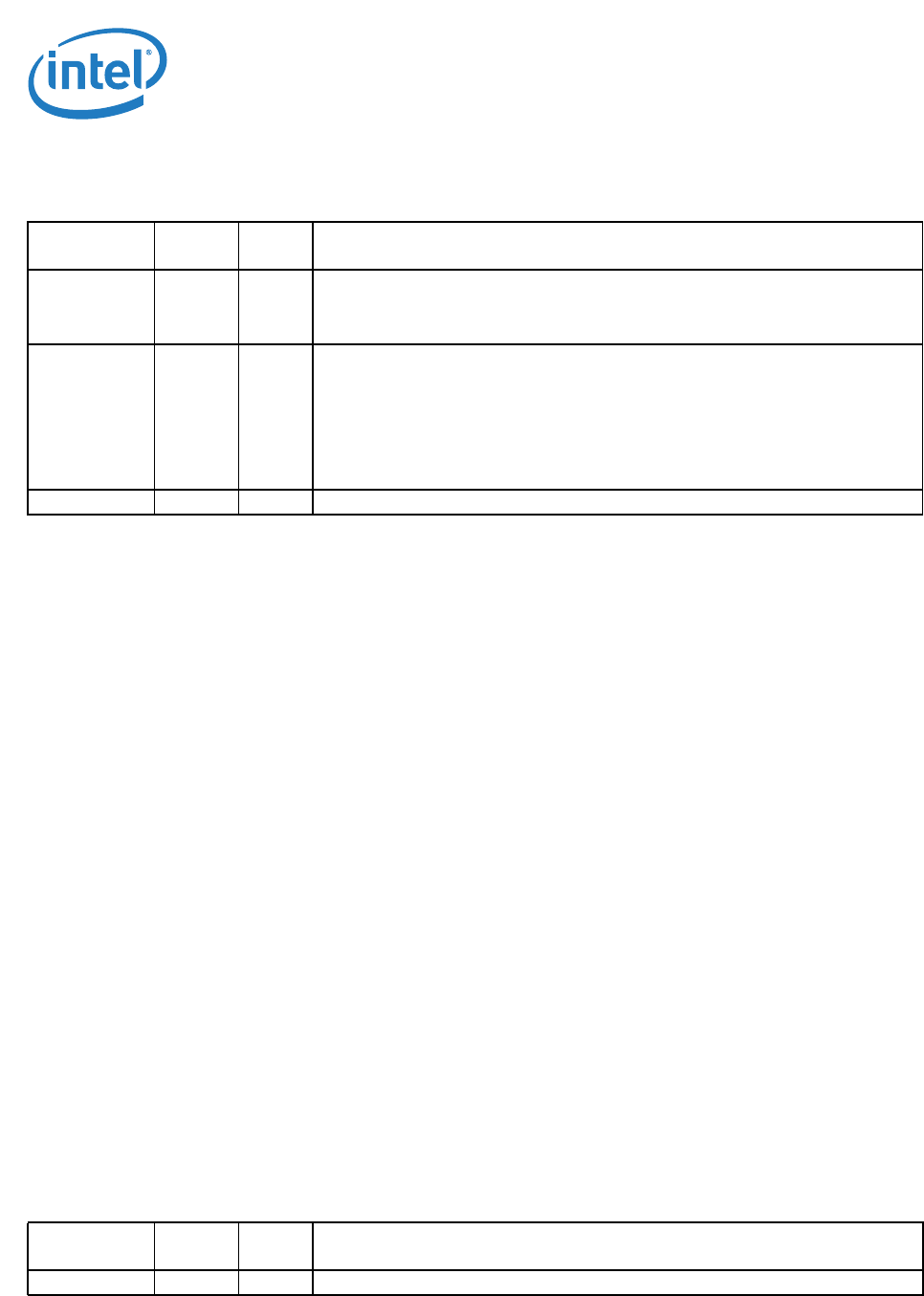

14.9.1 CRC Error Count - CRCERRS (04000h; RC)

Counts the number of receive packets with CRC errors. In order for a packet to be counted in this

register, it must pass address filtering and must be 64 bytes or greater (from <Destination Address>

through <CRC>, inclusively) in length. If receives are not enabled, then this register does not

increment.

Note: This counter also includes the alignment errors counted by the ALGNERRC register.

Field Bit(s)

Initial

Value

Description

DCA_DIS 0 1b DCA Disable

0b = DCA tagging is enabled for this port.

1b = DCA tagging is disabled for this port.

DCA_MODE 4:1 0h DCA Mode

000b = Data movement engine 1 is supported. The TAG field in the TLP header is based

on the following coding: bit 0 is DCA enable; bits 3:1 are CPU ID).

001b = Data movement engine 2 is supported. When DCA is disabled for a given

message, the TAG field is 0000,0000b. If DCA is enabled, the TAG is set per queue as

programmed in the relevant DCA Control register.

All other values are undefined.

Reserved 31:5 0h Reserved

Field Bit(s)

Initial

Value

Description

CEC 31:0 0b CRC error count