Intel

®

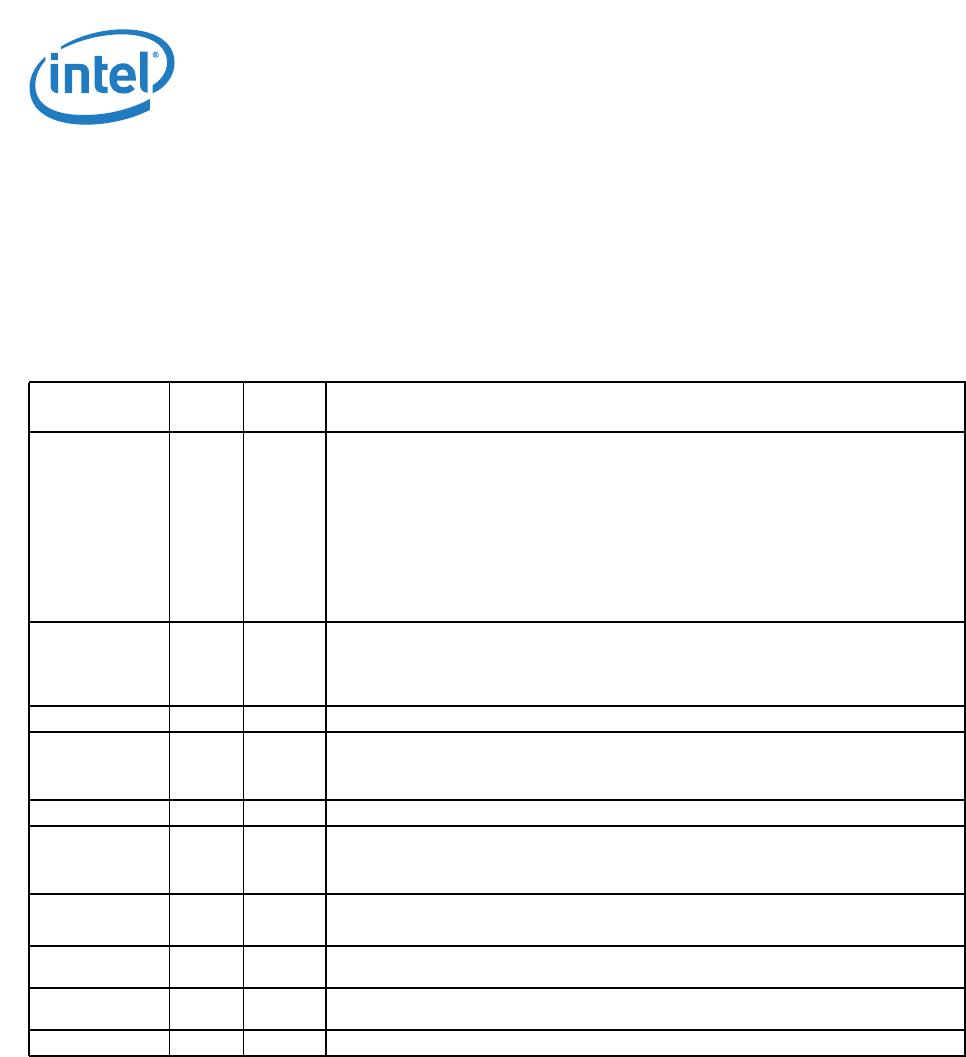

82575EB Gigabit Ethernet Controller — Tx DCA Control Registers - TXCTL (03814h + 100h

*n [n=0..3]; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

378 January 2011

14.4.2 Tx DCA Control Registers - TXCTL (03814h +

100h *n [n=0..3]; R/W)

• Queue0 - TXCTL0 (03814h)

• Queue1 - TXCTL1 (03914h)

• Queue2 - TXCTL2 (03A14h)

• Queue3 - TXCTL3 (03B14h)

14.5 Filter Registers

This section contains detailed descriptions for those registers associated with the 82575’s address filter

capabilities.

Field Bit(s)

Initial

Value

Description

CPUID 4:0 0h Physical ID

In a data movement engine 1 platform, the software device driver, upon discovery of

the physical CPU ID and CPU Bus ID, programs it into these bits for hardware to

associate Physical CPU and Bus ID with the adequate Tx queue. Bits 2:1 are Target

Agent IDs, bit 3 is the Bus ID. Bits 2:0 are copied into bits 3:1 in the TAG field of the

TLP headers of PCIe* messages.

In data movement engine 2 platforms, the software device driver programs a value,

based on the relevant APIC ID, corresponding to the adequate Tx queue. This value is

copied in the 4:0 bits of the DCA Preferences field in the TLP headers of PCIe*

messages.

TX Descriptor

DCA EN

5 0b Descriptor DCA Enable

When set, hardware enables DCA for all Tx descriptors written back into memory. When

cleared, hardware does not enable DCA for descriptor write-backs. This bit is cleared as

a default and also applies to head write-back when enabled.

Reserved 7:6 00b Reserved

TXdescRDNSen 8 0b Tx Descriptor Read No Snoop Enable

This bit must be reset to 0b to ensure correct functionality (unless the software device

driver has written this bit with a write-through instruction).

TXdescRDROEn 9 1b Tx Descriptor Read Relax Order Enable

TXdescWBNSen 10 0b Tx Descriptor Write-Back No Snoop Enable

This bit must be reset to 0b to ensure correct functionality of descriptor write-back.

Also applies to head write-back, when enabled.

RXdescWBROen 11 0b Tx Descriptor Write-Back Relax Order Enable

Applies to head write-back, when enabled.

TXDataRead

NSEn

12 0b Tx Data Read No Snoop Enable

TXDataRead

ROEn

13 1b Tx Data Read Relax Order Enable

Reserved 31:14 - Reserved