PHY Registers — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 319

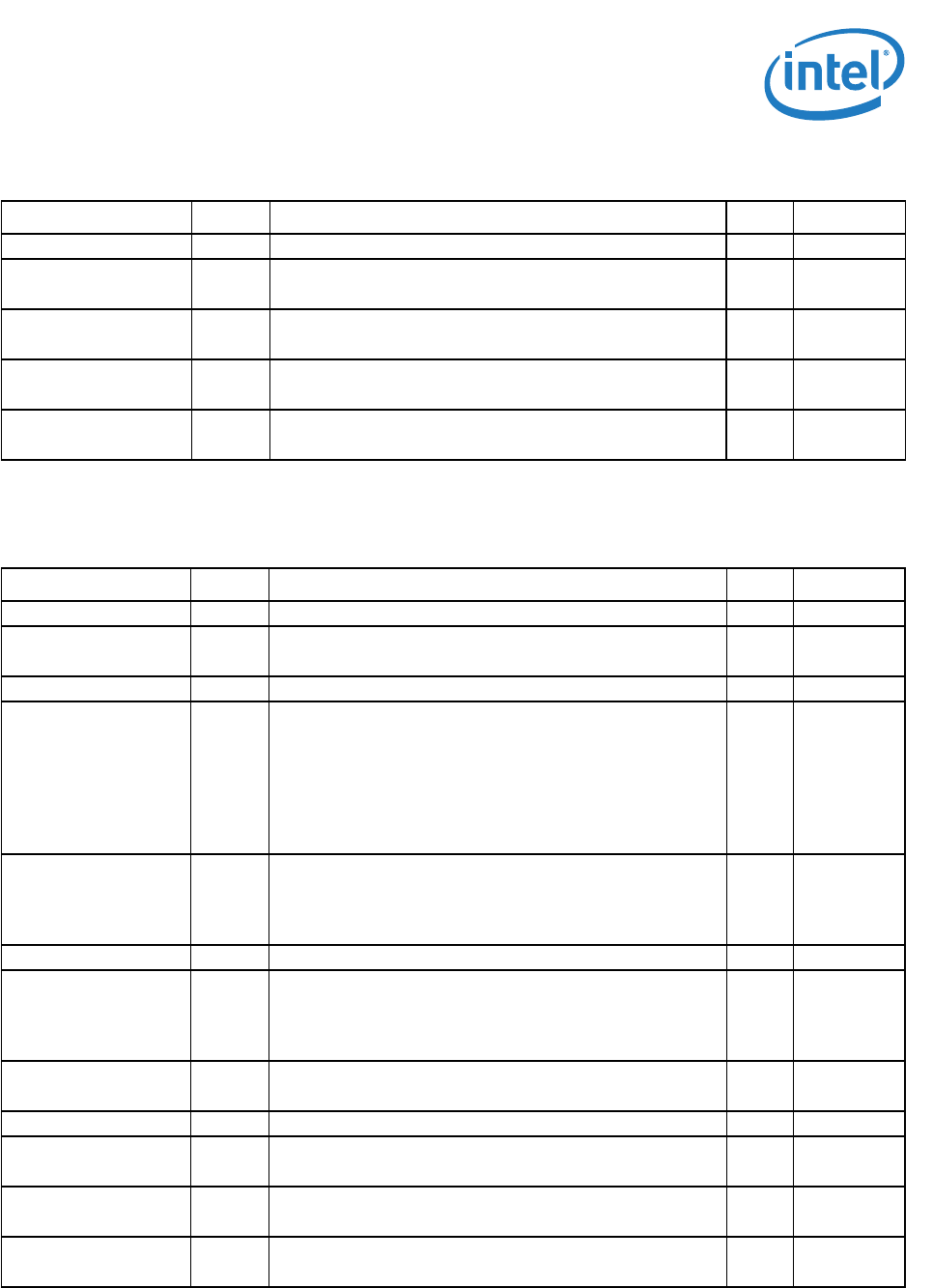

14.3.8.12 Extended Status Register - ESTATUS (15d; R)

14.3.8.13 Port Configuration Register - PCONF (16d; R/W)

Field Bit(s) Description Mode Default

Reserved 11:0 Reserved. Always read as 0b. RO 0b

1000BASE-T Half Duplex 12 1b = 1000BASE-T half duplex capable.

0b = not 1000BASE-T half duplex capable.

RO 1b

1000BASE-T Full Duplex 13 1b = 1000BASE-T full duplex capable.

0b = Not 1000BASE-T full duplex capable.

RO 1b

1000BASE-X Half

Duplex

14 1b =1000BASE-X half duplex capable.

0b = Not 1000BASE-X half duplex capable.

RO 0b

1000BASE-X Full Duplex 15 1b =1000BASE-X full duplex capable.

0b = Not 1000BASE-X full duplex capable.

RO 0b

Field Bit(s) Description Mode Default

Reserved 0 Always read as 0b. Write to 0b for normal operation. R/W 0b

Alternate NP Feature 1 1b = Enable alternate Auto-Negotiate next page feature.

0b = Disable alternate Auto-Negotiate next page feature.

R/W 0b

Reserved 3:2 Always read as 0b. Write to 0b for normal operation. R/W 0b

Auto MDIX Parallel

Detect Bypass

4 Auto_MDIX Parallel Detect Bypass. Bypasses the fix to IEEE

auto-MDIX algorithm for the case where the PHY is in forced-

speed mode and the link partner is auto-negotiating.

1b = Strict 802.3 Auto-MDIX algorithm.

0b = Auto-MDIX algorithm handles Auto-Negotiation disabled

modes. This is accomplished by lengthening the auto-MDIX

switch timer before attempting to swap pairs on the first time

out.

R/W 0b

PRE_EN 5 Preamble Enable

0b = Set RX_DV high coincident with SFD.

1b = Set RX_DV high and RXD = preamble (after CRS is

asserted).

R/W 1b

Reserved 6 Always read as 0b. Write to 0b for normal operation. R/W 0b

Smart Speed 7 1b = Smart Speed selection enabled.

0b = Smart Speed selection disabled.

Note: The default of this bit is determined by the EEPROM

speed bit (word 21h, bit 5).

R/W 0b

TP Loopback (10BASE-

T)

8 1b = Disable TP loopback during half-duplex operation.

0b = Normal operation.

R/W 1b

Reserved 9 Always read as 0b. Write to 0b for normal operation. R/W 0b

Jabber (10BASE-T) 10 1b = Disable jabber.

0b = Enable jabber.

R/W 0b

Bypass 4B5B (100BASE-

TX)

11 1b = Bypass4B5B encoder and decoder.

0b = Normal operation.

R/W 0b

Bypass Scramble

(100BASE-TX)

12 1b = Bypass scrambler and descrambler.

0b = Normal operation.

R/W 0b