Power-State Transitions Timing — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 227

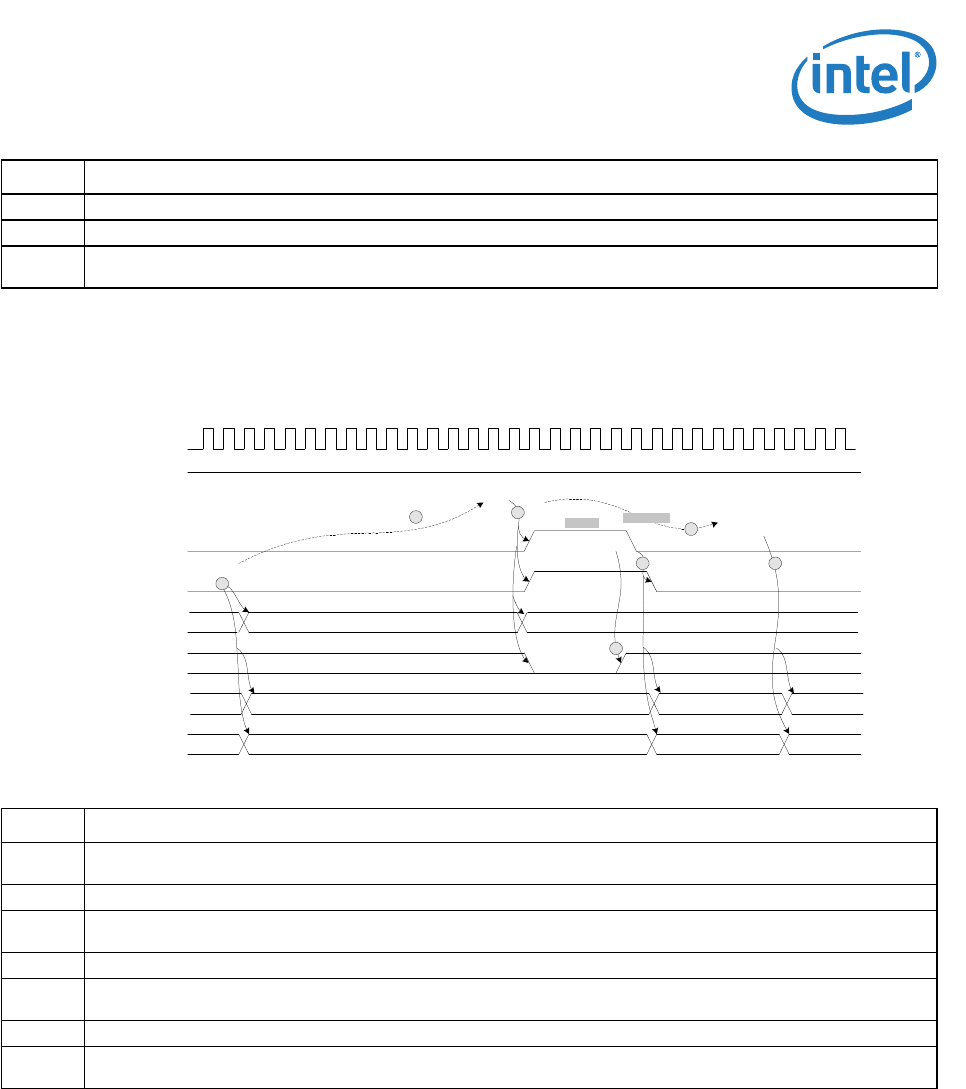

7.4.2.2 Transition from D0a to D3 and Back without PE_RST_N

13 A first PCIe* configuration access might arrive after t

pgcfg

from PE_RST_N de-assertion.

14 A first PCIe* configuration response can be sent after t

pgres

from PE_RST_N de-assertion.

15 Writing a 1b to the Memory Access Enable bit in the PCI Command Register transitions the 82575 from D0u to D0

state.

Notes

1 Writing 11b to the Power State field of the Power Management Control/Status Register (PMCSR) transitions the 82575

to D3.

2 The system keeps the 82575 in D3 for an arbitrary amount of time.

3 To exit D3, the system writes 00b to the Power State field of the Power Management Control/Status Register

(PMCSR).

4 APM wake up or SMB mode can be enabled based on the EEPROM contents.

5 After reading the EEPROM, the reset to the PHY is de-asserted. The PHY operates at a reduced speed if APM wake up

or SMB is enabled. Otherwise, it is powered down.

6 The system can delay an arbitrary time before enabling memory access.

7 Writing a 1b to the Memory Access Enable bit or to the I/O Access Enable bit in the PCI Command Register transitions

the 82575 from D0u to D0 and returns the PHY to full power and full speed operation.

Notes

PCIe*

Reference Clock

PCIe* PwrGd

PHY Reset

PCIe* Link

Reading EEPROM Read EEPROM

DState D3 D0u D0

Wakeup Enabled

Memory Access Enable

L0

D3 write

APM / SMBusAny mode

D0 Write

D0a

2

L1

L0

PHY Power State

full FullPower Managed Power Managed

tee

1

3

4

5

6

7

td0mem