Memory and I/O Address Decoding — Intel

®

82575EB Gigabit Ethernet Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 289

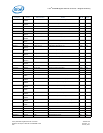

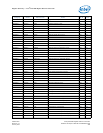

Table 87. Field Attributes

14.1.1 Memory and I/O Address Decoding

14.1.1.1 Memory-Mapped Access to Internal Registers and

Memories

The internal registers and memories can be accessed as direct memory-mapped offsets from the base

address register (BAR0 see Section 6.6.4).

14.1.1.2 Memory-Mapped Access to FLASH

The external Flash can be accessed using direct memory-mapped offsets from the Flash Base Address

register (BAR1 see Section 6.6.4). The Flash is only accessible if enabled through the EEPROM

Initialization Control Word, and if the Flash Base Address register contains a valid (non-zero) base

memory address. For accesses, the offset from the Flash BAR corresponds to the offset into the flash

actual physical memory space.

14.1.1.3 Memory-Mapped Access to MSI-X Tables

The MSI-X tables can be accessed as direct memory-mapped offsets from the Base Address register

(BAR3 see Section 6.6.4). See Section 14.1.1.4 for the appropriate offset for each specific internal

register.

Attribute Description

RW Read-Write field: Register bits are read-write and can be either set or cleared by software to the desired state.

RWS Read-Write Status field: Register bits are read-write and can be either set or cleared by software to the desired

state. However, the value of this field might be changed by hardware to reflect a status change.

RO Read-only register: Register bits are read-only and cannot be altered by software. Register bits can be

initialized by hardware mechanisms such as pin strapping or serial EEPROM or reflect status of the hardware

state.

R/W1C Read-only status, Write-1b-to-clear status register: Register bits indicate status when read, a set bit indicating

a status event can be cleared by writing a 1b. Writing a 0b to R/W1C bits has no effect. These bits are

considered as status bits.

RSV Reserved. These fields should not be written.

RC Read-only status, Read-to-clear status register: Register bits indicate status when read, a set bit indicating a

status event is cleared by reading it.

SC Self Clear field: a command field that is self clearing. These fields are always read as 0b.

WO Write only field: a command field that can not be read, These fields read value is undefined.

RC/W1C Read-only status, Write-1b-to-clear status register: Read-to-clear status register Register bits indicate status

when read, a set bit indicating a status event can be cleared by writing a 1b or by reading the register. Writing

a 0b to RC/W1C bits has no effect.

RS Read Set – this is the attribute used for Semaphore bits. These bits are set by read in case the previous value

was 0b. In this case the read value is 0b; otherwise the read value is 1b. Cleared by writing 0b.