Manageability Flash Read Counter - FLMNGCNT (1020h; R/W) — Intel

®

82575EB Gigabit Ethernet

Controller

324632-003 Intel

®

82575EB Gigabit Ethernet Controller

Revision: 2.1 Software Developer’s Manual and EEPROM Guide

January 2011 337

(101Ch; R/W)

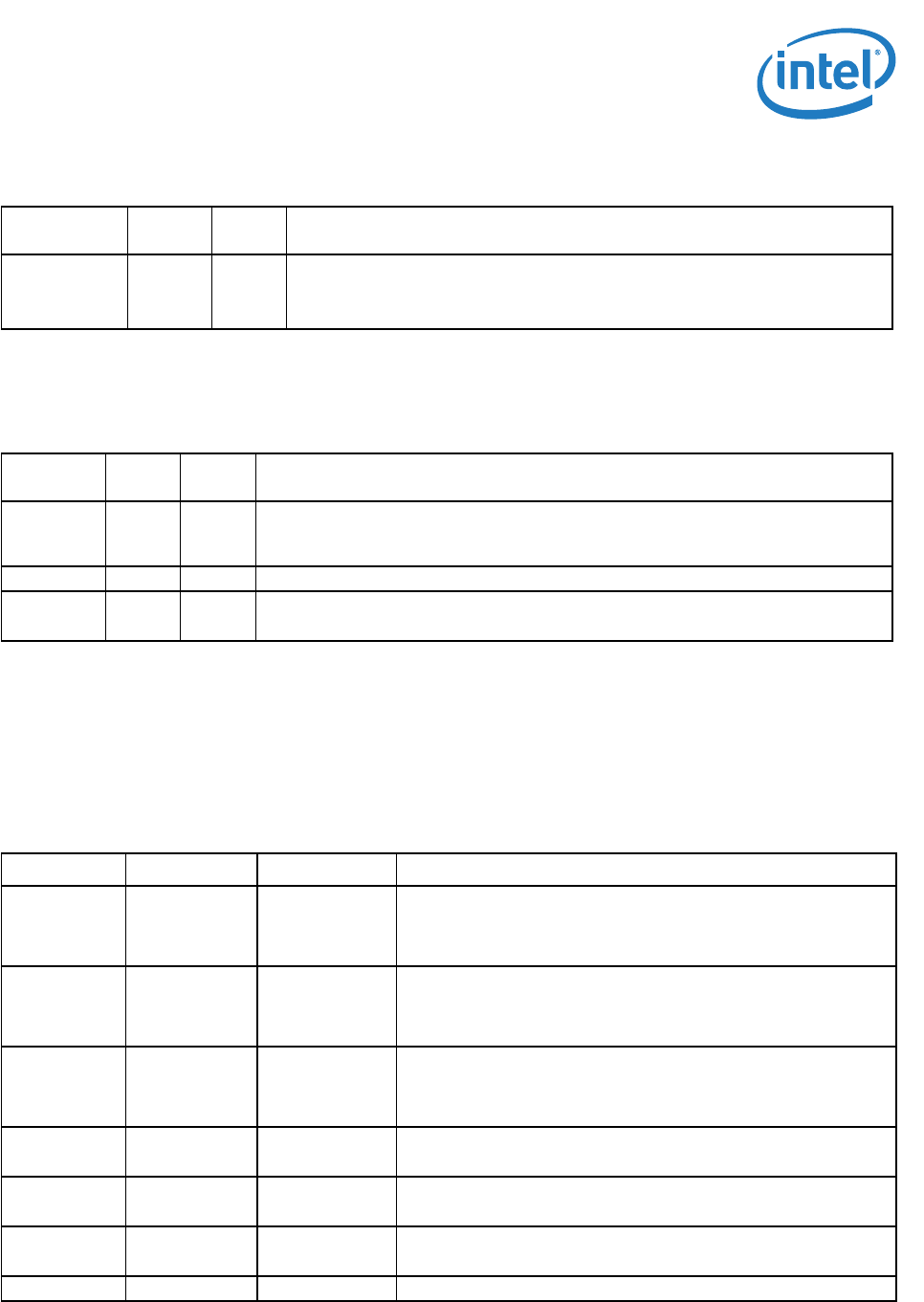

14.3.28 Manageability Flash Read Counter - FLMNGCNT

(1020h; R/W)

14.3.29 EEPROM Auto Read Bus Control - EEARBC

(01024h; R/W)

In EEPROM-less implementations, this register is used to program the 82575 the same way it should be

programmed if an EEPROM was present.

Note: A separate Application Note is required to enable implementing the software device driver.

Field Bit(s)

Initial

Value

Description

DATA 31:0 00h Read/write Data

On read transactions, this register contains the data returned from the Flash read.

On write transactions, bits 7:0 are written to the Flash.

Field Bit(s)

Initial

Value

Description

Abort 31 0b Abort

Writing a 1b to this bit aborts the current burst read operation. It is self-cleared by the

Flash interface block when the Abort command is executed.

Reserved 30:25 00h Reserved

RDCNT 24:0 00h Read Counter

This counter holds the size of the Flash burst read in Dwords.

Field Bit(s) Initial Value Description

VALID_CORE 0 0b Valid Write Active to Core 0

Write strobe to Core 0. Firmware/software sets this bit for write

access. Software should clear this bit to terminate the write

transaction.

VALID_CORE1 1 0b Valid Write Active to Core 1

Write strobe to Core 1. Firmware/software sets this bit for write

access. Software should clear this bit to terminate the write

transaction.

VALID_

COMMON

2 0b Valid Write Active to Common

Write strobe to Common. Firmware/software sets this bit for write

access. Software should clear this bit to terminate the write

transaction.

Reserved 3 0b Reserved

Reads as 0b.

ADDR 12:4 0h Write Address

This field specifies the 16-bit word address of the EEPROM data.

Reserved

15:13

0h 0b Reserved

Reads as 0b.

DATA 31:16 0h Data written into the EEPROM auto read bus.