Intel

®

82575EB Gigabit Ethernet Controller — GIOANACTL3 (05B40h; R/W)

Intel

®

82575EB Gigabit Ethernet Controller 324632-003

Software Developer’s Manual and EEPROM Guide Revision: 2.1

410 January 2011

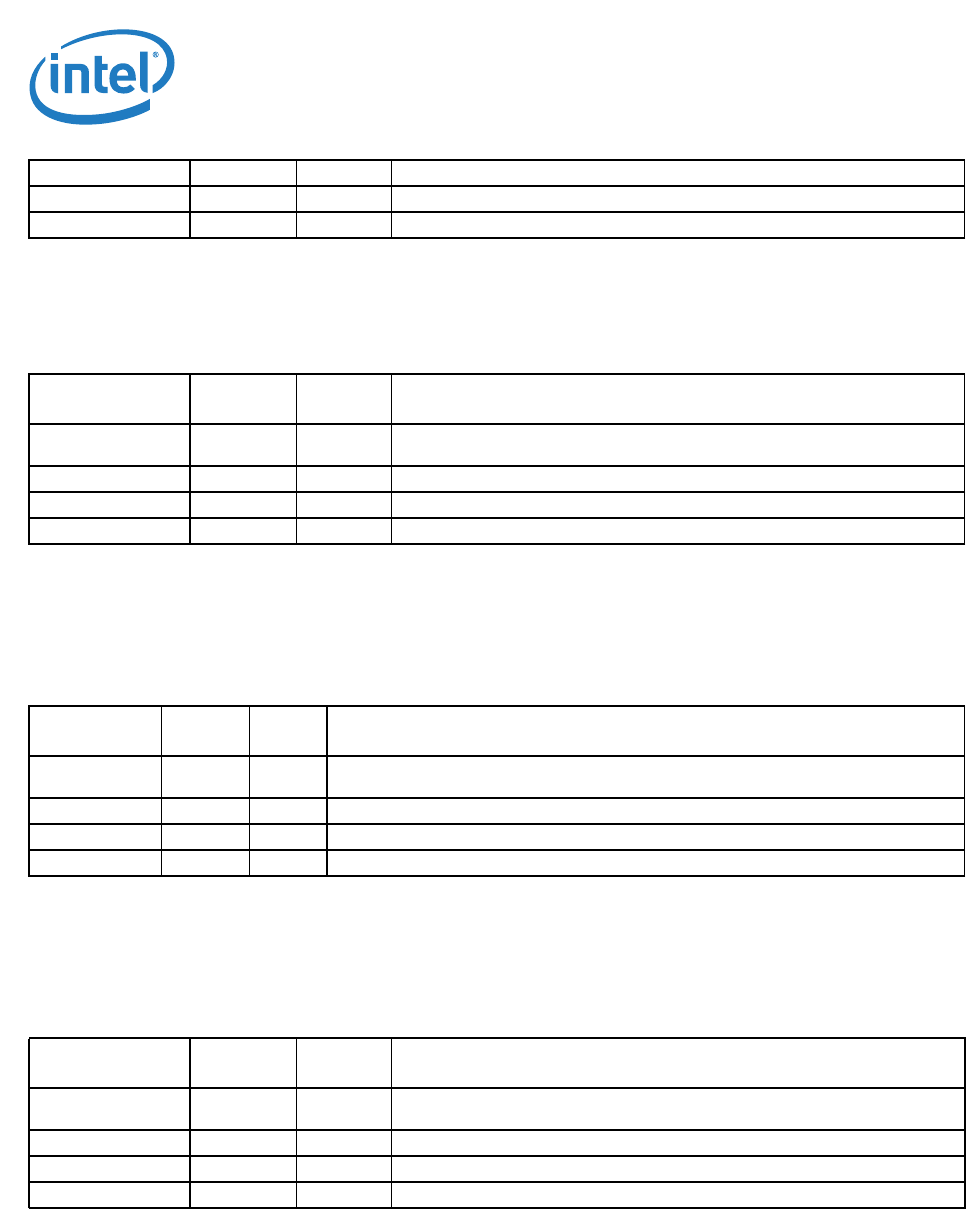

14.8.15 GIOANACTL3 (05B40h; R/W)

Firmware uses this register for analog circuit configuration.

14.8.16 SerDes/CCM/PCIe* CSR - GIOANACTLALL

(05B44h; R/W)

Firmware uses this register for analog circuit configuration.

14.8.17 SerDes/CCM/PCIe* CSR - CCMCTL (05B48h; R/

W)

Firmware uses this register for analog circuit configuration.

14.8.18 SerDes/CCM/PCIe* CSR - SCCTL (05B4Ch; R/

W)

Firmware uses this register for analog circuit configuration.

Reserved 30:16 0b Reserved.

Address 15:8 0b Address to SerDes.

Data 7:0 0b Data to SerDes.

Field Bit(s)

Initial

Value

Description

Done Indication 31 1b When a write operation completes this bit is set to 1b indicating that new data

can be written. This bit is over written to 0b by new data.

Reserved 30:16 0b Reserved.

Address 15:8 0b Address to SerDes.

Data 7:0 0b Data to SerDes.

Field Bit(s)

Initial

Value

Description

Done

Indication

31 1b When a write operation completes this bit is set to 1b indicating that new data can be

written. This bit is over written to 0b by new data.

Reserved 30:16 0b Reserved.

Address 15:8 0b Address to SerDes.

Data 7:0 0b Data to SerDes.

Field Bit(s)

Initial

Value

Description

Done Indication 31 1b When a write operation completes this bit is set to 1b indicating that new data

can be written. This bit is over written to 0b by new data.

Reserved 30:16 0b Reserved.

Address 15:8 0b Address to SerDes.

Data 7:0 0b Data to SerDes.