Section 25 Electrical Characteristics

Rev. 4.00 Sep. 14, 2005 Page 954 of 982

REJ09B0023-0400

25.3.8 Peripheral Module Signal Timing

Table 25.9 Peripheral Module Signal Timing

Conditions: V

CC

Q = 3.0 V to 3.6 V, V

CC

= 1.8 V ± 5%, AV

CC

= 3.0 V to 3.6 V,

V

SS

= V

SS

Q = AV

SS

= 0 V, Ta = −40°C to +85°C

Module Item Symbol Min. Max. Unit Figure(s)

SCIF Input clock cycle (synchronous) 16 — t

Pcyc

25.42

(asynchronous)

t

Scyc

4 — t

Pcyc

25.42

Input clock rising time t

SCKR

— 1.5 t

Pcyc

25.42

Input clock falling time t

SCKF

— 1.5 t

Pcyc

25.42

Input clock width t

SCKW

0.4 0.6 t

Scyc

25.42

Transmit data delay time

(synchronous)

t

TXD

— 3 t

Pcyc

+ 15 ns 25.43

Receive data setup time

(synchronous)

t

RXS

4 t

Pcyc

+ 15 — ns 25.43

Receive data hold time

(synchronous)

t

RXH

100 — ns 25.43

PORT Output data delay time t

PORTD

— 100

Input data setup time t

PORTS2

100 —

Input data hold time t

PORTH2

100 —

ns 25.44

DMAC DREQ setup time t

DREQ

8 —

DREQ hold time t

DREQH

8 —

25.45

DACK, TEND delay time t

DACD

— 12

ns

25.46

Note: * t

Pcyc

indicate Pclock cycle.

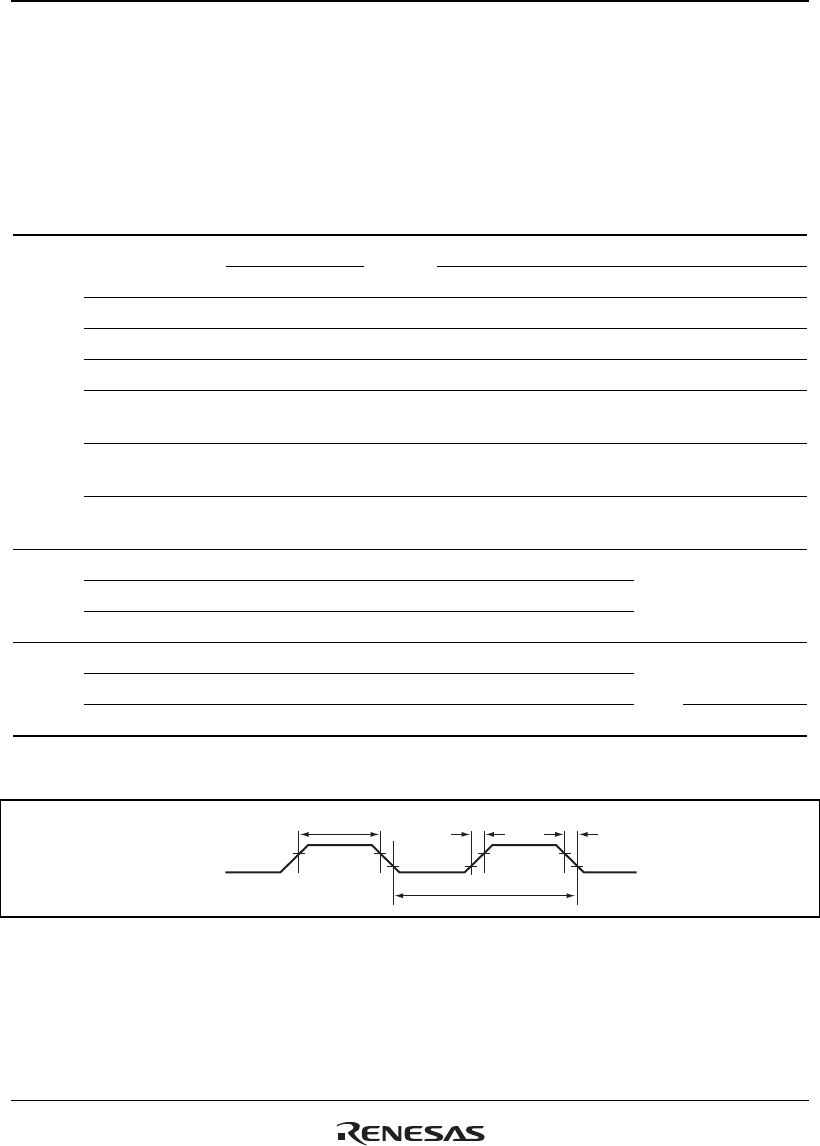

t

SCKW

t

SCKR

t

SCKF

t

Scyc

SCK

Figure 25.42 SCK Input Clock Timing