Section 2 CPU

Rev. 4.00 Sep. 14, 2005 Page 83 of 982

REJ09B0023-0400

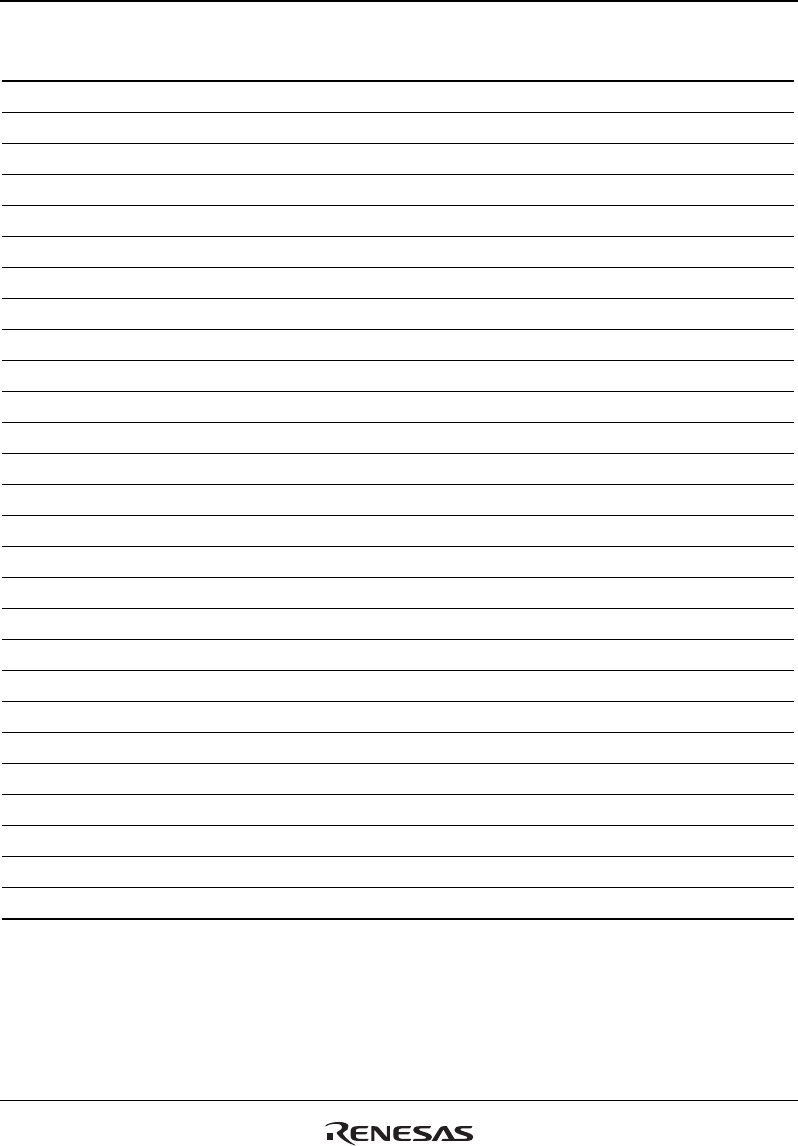

Instruction

Instruction Code

Operation

Execution

States

T Bit

STS.L DSR,@-Rn 0100nnnn01100010 Rn – 4 → Rn, DSR → (Rn) 1

STS.L A0,@-Rn 0100nnnn01110010 Rn – 4 → Rn, A0 → (Rn) 1

STS.L X0,@-Rn 0100nnnn10000010 Rn – 4 → Rn, X0 → (Rn) 1

STS.L X1,@-Rn 0100nnnn10010010 Rn – 4 → Rn, X1 → (Rn) 1

STS.L Y0,@-Rn 0100nnnn10100010 Rn – 4 → Rn, Y0 → (Rn) 1

STS.L Y1,@-Rn 0100nnnn10110010 Rn – 4 → Rn, Y1 → (Rn) 1

STC.L MOD,@-Rn 0100nnnn01010011 Rn – 4 → Rn, MOD → (Rn) 1

STC.L RS,@-Rn 0100nnnn01100011 Rn – 4 → Rn, RS → (Rn) 1

STC.L RE,@-Rn 0100nnnn01110011 Rn – 4 → Rn, RE → (Rn) 1

LDS.L @Rn+,DSR 0100nnnn01100110 (Rn) → DSR, Rn + 4 → Rn 1

LDS.L @Rn+,A0 0100nnnn01110110 (Rn) → A0, Rn + 4 → Rn 1

LDS.L @Rn+,X0 0100nnnn10000110 (Rn) → X0, Rn + 4 → Rn 1

LDS.L @Rn+,X1 0100nnnn10010110 (Rn) → X1, Rn + 4 → Rn 1

LDS.L @Rn+,Y0 0100nnnn10100110 (Rn) → Y0, Rn + 4 → Rn 1

LDS.L @Rn+,Y1 0100nnnn10110110 (Rn) → Y1, Rn + 4 → Rn 1

LDC.L @Rn+,MOD 0100nnnn01010111 (Rn) → MOD, Rn + 4 → Rn 4

LDC.L @Rn+,RS 0100nnnn01100111 (Rn) → RS, Rn + 4 → Rn 4

LDC.L @Rn+,RE 0100nnnn01110111 (Rn) → RE, Rn + 4 → Rn 4

LDS Rn,DSR 0100nnnn01101010 Rn → DSR 1

LDS Rn,A0 0100nnnn01111010 Rn → A0 1

LDS Rn,X0 0100nnnn10001010 Rn → X0 1

LDS Rn,X1 0100nnnn10011010 Rn → X1 1

LDS Rn,Y0 0100nnnn10101010 Rn → Y0 1

LDS Rn,Y1 0100nnnn10111010 Rn → Y1 1

LDC Rn,MOD 0100nnnn01011110 Rn → MOD 4

LDC Rn,RS 0100nnnn01101110 Rn → RS 4

LDC Rn,RE 0100nnnn01111110 Rn → RE 4