Section 3 DSP Operation

Rev. 4.00 Sep. 14, 2005 Page 99 of 982

REJ09B0023-0400

Section 3 DSP Operation

3.1 Data Operations of DSP Unit

3.1.1 ALU Fixed-Point Operations

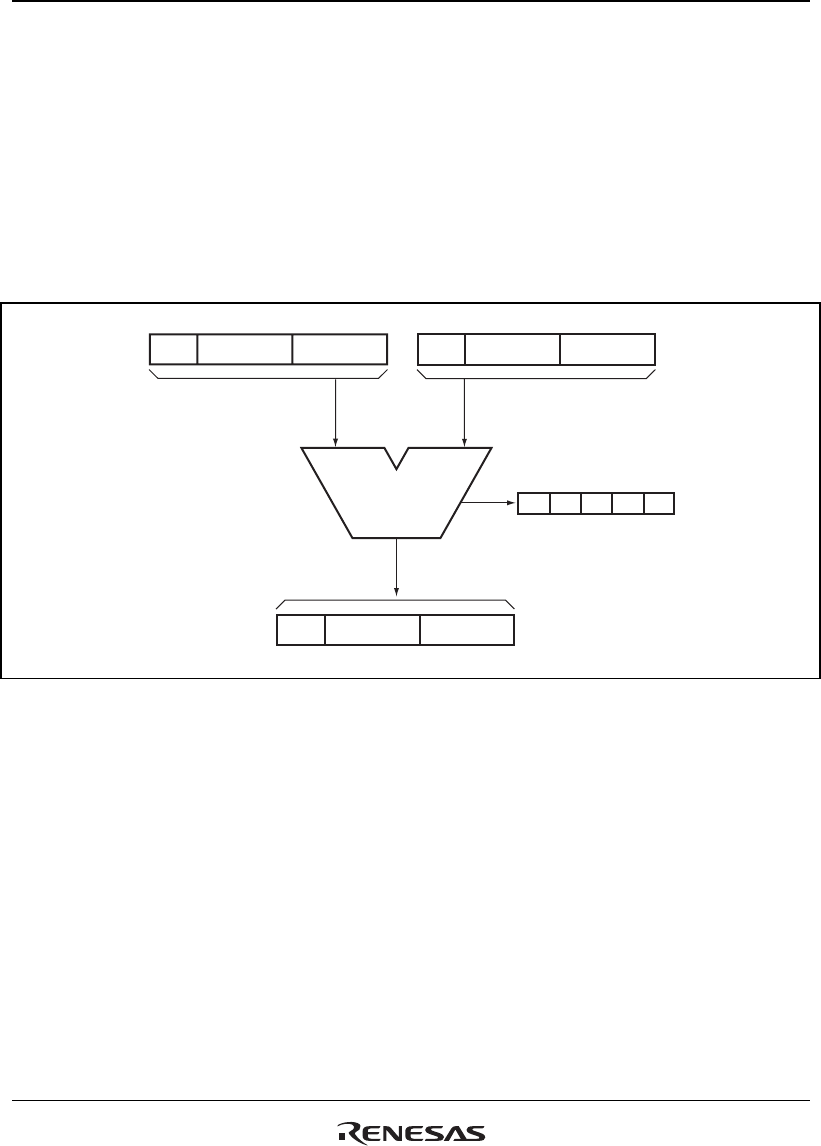

Figure 3.1 shows the ALU arithmetic operation flow. Table 3.1 shows the variation of this type of

operation and table 3.2 shows the correspondence between each operand and registers.

39 31 0

Source 1

0

Destination

ALU

DSR

GT Z N V

DC

0

Source 2

Guard

39 31

Guard

Guard

39 31

Figure 3.1 ALU Fixed-Point Arithmetic Operation Flow

Note: The ALU fixed-point arithmetic operations are basically 40-bit operation; 32 bits of the

base precision and 8 bits of the guard-bit parts. So the signed bit is copied to the guard-bit

parts when a register not providing the guard-bit parts is specified as the source operand.

When a register not providing the guard-bit parts is specified as a destination operand, the

lower 32 bits of the operation result are input into the destination register.

ALU fixed-point operations are executed between registers. Each source and destination

operand are selected independently from one of the DSP registers. When a register

providing guard bits is specified as an operand, the guard bits are activated for this type of

operation. These operations are executed in the DSP stage, as shown in figure 3.2. The

DSP stage is the same stage as the MA stage in which memory access is performed.